# Jaipur Engineering College & Research Centre, Jaipur

**Department of Electronics & Communication Engineering**

Session (2020-21)

### <u>Notes File</u>

MECHATRONIC SYSTEMS (5ME3-07)

Prepared By: Mr.Devedra Sharma (AP, Dept. of ECE)

**MECHATRONIC SYSTEMS 5ME3-01**

**Page** 1

# RAJASTHAN TECHNICAL UNIVERSITY, KOTA Syllabus 3<sup>rd</sup> Year - V Semester: B.Tech. : Mechanical Engineering

#### 5ME3-01: MECHATRONIC SYSTEMS

| Credit: 2 Max. Marks: 100(IA: 20, ETE<br>2L+0T+0P End Term Exam: 2 E |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SN                                                                   | CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Hours |

| 1                                                                    | Introduction: Objective, scope and outcome of the course.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1     |

| 2                                                                    | Overview of Mechatronics: Historical perspective, Definition,<br>Applications, Block diagram of Mechatronic system, Functions of<br>Mechatronics Systems, Systems Engineering, Verification Vs<br>Validation, Benefits of mechatronics in manufacturing.                                                                                                                                                                                                                                                                                                                                                                                                 | 2     |

|                                                                      | Electrical and Electronic Systems: Electrical circuits and<br>Kirchhoff's laws, Network Theorems and AC circuit Analysis,<br>Transformers, Analog Devices, Signal Conditioning, Digital<br>Electronics, Data Acquisition systems.                                                                                                                                                                                                                                                                                                                                                                                                                        | з     |

| 3                                                                    | Modeling, Analysis and Control of Physical Systems: Basics of<br>System Modeling; LTI and LTV systems, Need for modeling, Types of<br>modeling, Steps in modeling, Building blocks of models, Modelling<br>of one and two degrees of freedom systems, Modeling of Electro-<br>mechanical systems, Mechanical Systems, Fluid systems,<br>Thermal systems; Dynamic Responses, System Transfer<br>Functions, State Space Analysis and System Properties, Stability<br>Analysis using Root Locus Method, Stability Analysis using Bode<br>Flots, FID Controllers (with and without Time Delay)                                                               | 5     |

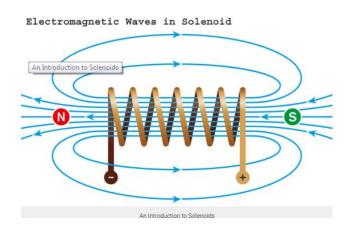

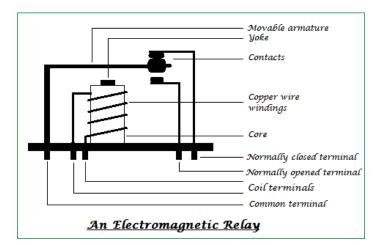

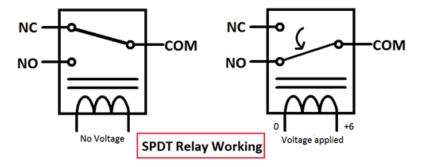

| 4                                                                    | Sensors and Actuators: Static characteristics of sensors and<br>actuators, Position, Displacement and Proximity Sensors, Porce<br>and torque sensors, Pressure sensors, Flow sensors, Temperature<br>sensors, Acceleration sensors, Level sensors, Light sensors, Smart<br>material sensors, Micro and Nano sensors, Selection criteria for<br>sensors, Actuators: Electrical Actuators (Solenoids, Relays, Diodes,<br>Thyristors, Triacs, BJT, FET, DC motor, Servo motor, BLDC motor, AC<br>motor, Stepper motors), Hydraulic and Pneumatic actuators,<br>Design of Hydraulic and Pneumatic circuits, Piezoelectric<br>actuators, Shape memory alloys, | 7     |

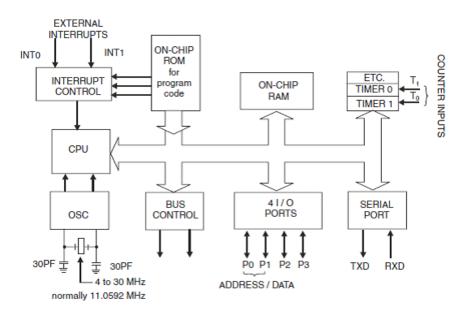

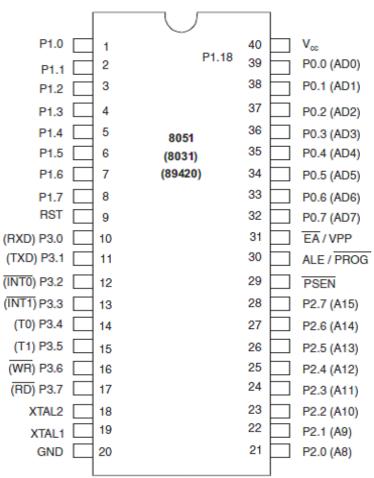

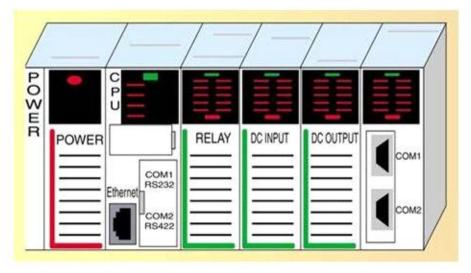

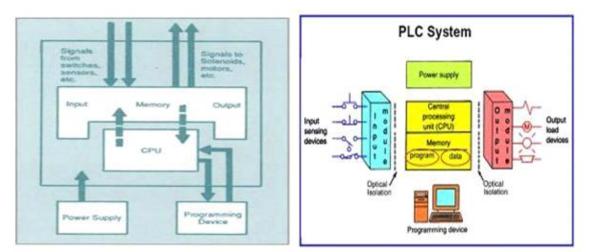

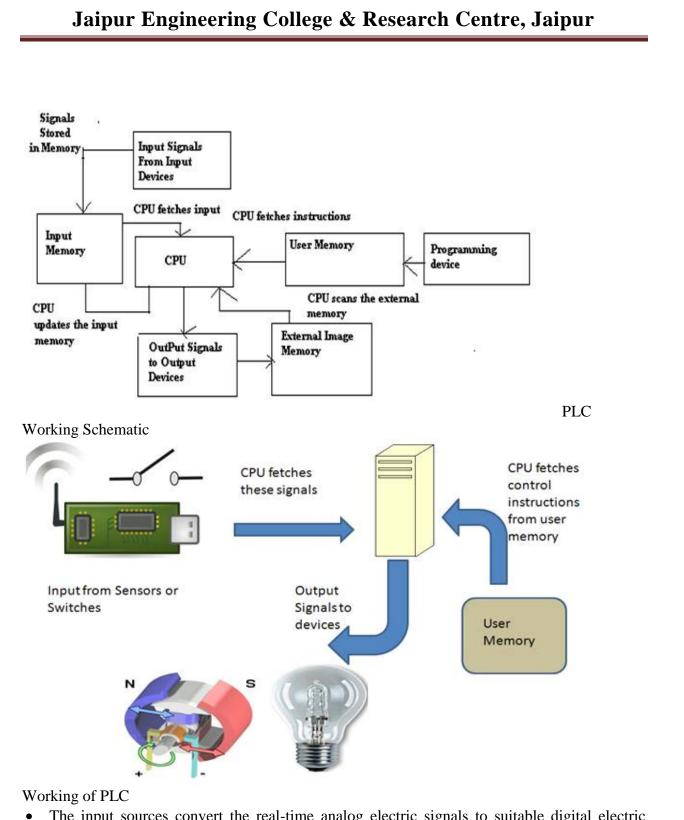

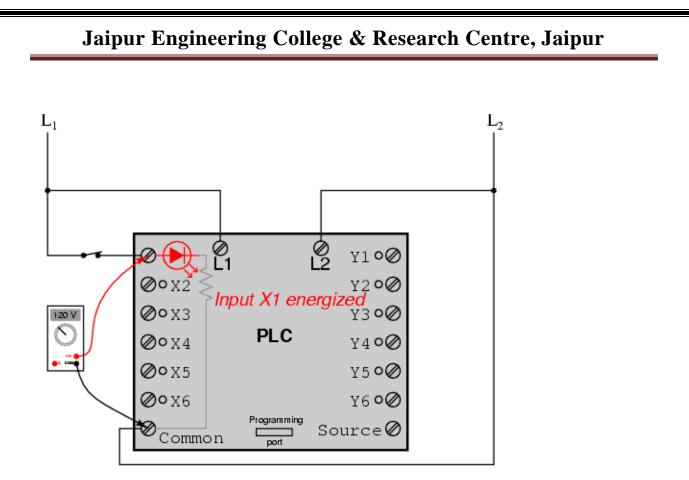

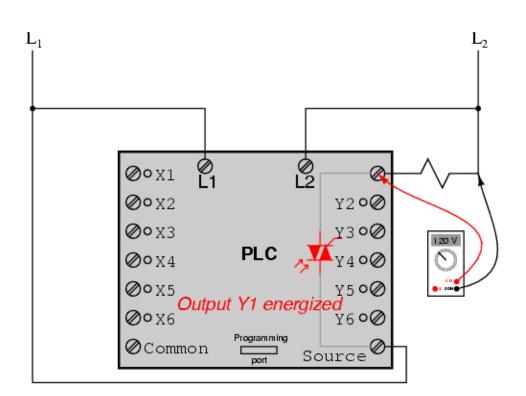

| 5                                                                    | Microprocessors, Microcontrollers and Programmable Logic<br>Controllers: Logic Concepts and Design, System Interfaces,<br>Communication and Computer Networks, Fault Analysis in<br>Mechatronic Systems, Synchronous and Asynchronous<br>Sequential Systems, Architecture, Microcontrollers.                                                                                                                                                                                                                                                                                                                                                             | 3     |

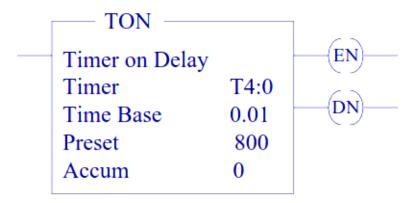

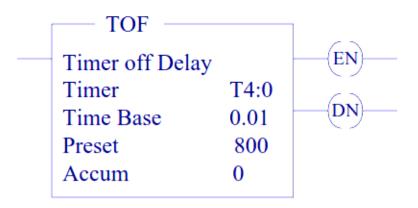

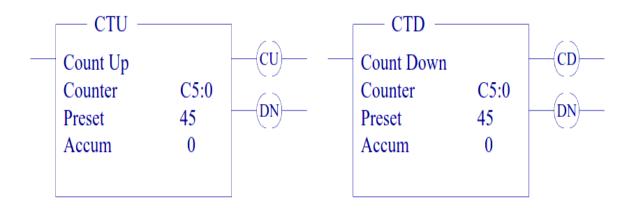

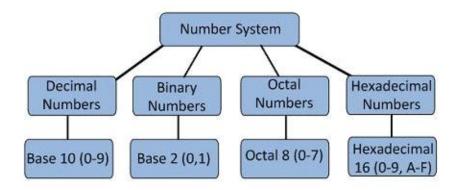

| 6                                                                    | Programmable Logic Controllers (PLCs): Architecture, Number Systems<br>Basics of PLC Programming, Logics, Timers and Counters,<br>Application on real time industrial automation systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4     |

|                                                                      | Case Studies: Design of pick and place robot, Car engine<br>management system, Automated manufacturing system, Automatic<br>camera, Automatic parking system, Safety devices and systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3     |

|                                                                      | TOTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28    |

#### UNIT 1 Overview of Mechatronics:

Historical perspective, Definition, Applications, Block diagram of Mechatronic system, Functions of Mechatronics Systems, Systems Engineering, Verification Vs Validation, Benefits of mechatronics in manufacturing.

Electrical and Electronic Systems: Electrical circuits and Kirchhoff's laws, Network Theorems and AC circuit Analysis, Transformers, Analog Devices, Signal Conditioning, Digital Electronics, Data Acquisition systems

#### UNIT 2

Modeling, Analysis and Control of Physical Systems: Basics of System Modeling: LTI and LTV systems, Need for modeling, Types of modeling, Steps in modeling, Building blocks of models, Modelling of one and two degrees of freedom systems, Modeling of Electro-mechanical systems, Mechanical Systems, Fluid systems, Thermal systems; Dynamic Responses, System Transfer Functions, State Space Analysis and System Properties, Stability Analysis using Root Locus Method, Stability Analysis using Bode Plots, PID Controllers (with and without Time Delay

#### UNIT 3

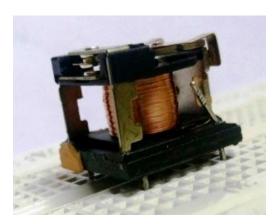

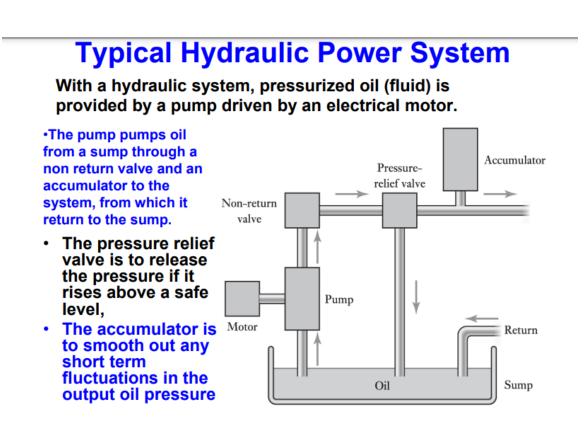

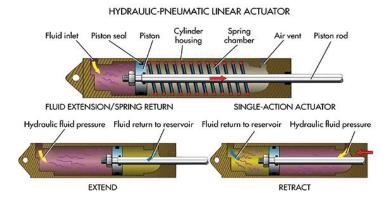

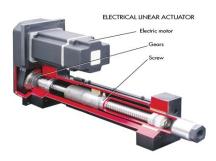

Sensors and Actuators: Static characteristics of sensors and actuators, Position, Displacement and Proximity Sensors, Force and torque sensors, Pressure sensors, Flow sensors, Temperature sensors, Acceleration sensors, Level sensors, Light sensors, Smart material sensors, Micro and Nano sensors, Selection criteria for sensors, Actuators: Electrical Actuators (Solenoids, Relays, Diodes, Thyristors, Triacs, BJT, FET, DC motor, Servo motor, BLDC motor, AC motor, Stepper motors), Hydraulic and Pneumatic actuators, *Design of Hydraulic and Pneumatic circuits, Piezoelectric actuators, Shape memory alloys.*

#### UNIT 4

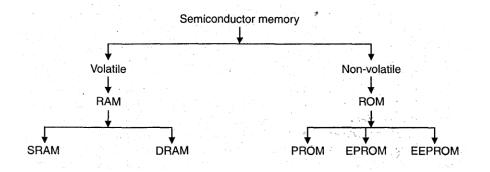

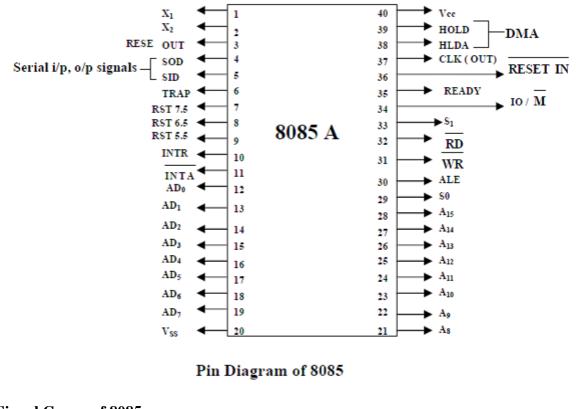

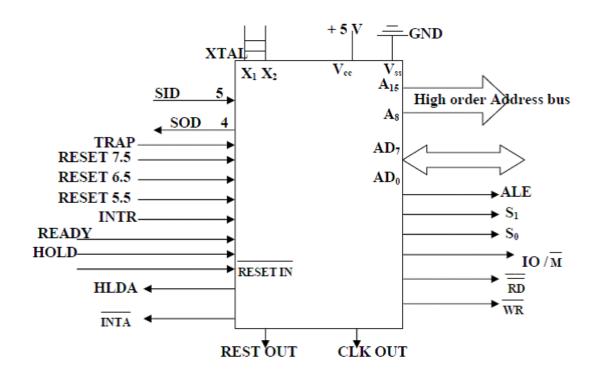

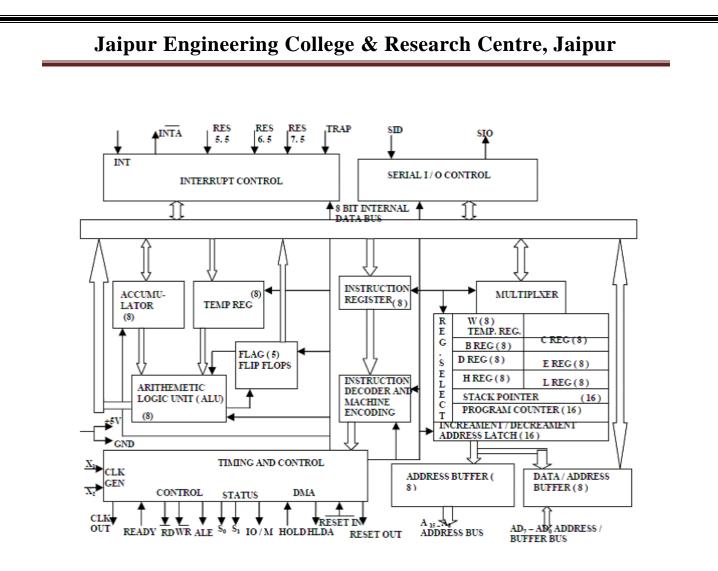

Microprocessors, Microcontrollers and Programmable Logic Controllers: Logic Concepts and Design, System Interfaces, Communication and Computer Networks, Fault Analysis in Mechatronic Systems, Synchronous and Asynchronous Sequential Systems, Architecture, **Microcontrollers**.

#### Unit 5

Programmable Logic Controllers (PLCs): Architecture, Number Systems Basics of PLC Programming, Logics, Timers and Counters, Application on real time industrial automation systems .Case Studies: Design of pick and place robot, Car engine management system, Automated manufacturing system, Automatic camera, Automatic parking system, Safety devices and systems

**UNIT 1** Overview of Mechatronics:

Historical perspective, Definition, Applications, Block diagram of Mechatronic system, Functions of Mechatronics Systems, Systems Engineering, Verification Vs Validation, Benefits of mechatronics in manufacturing.

Electrical and Electronic Systems: Electrical circuits and Kirchhoff's laws, Network Theorems and AC circuit Analysis, Transformers, Analog Devices, Signal Conditioning, Digital Electronics, Data Acquisition systems

#### UNIT-1

#### **Overview of Mechatronics**

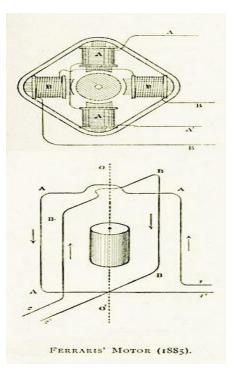

**INTRODUCTION:**The word Mechatronics was first introduced by the senior engineer of a Japanese company, Yaskawa, in 1969. The company was granted trademark rights on the word in 1971. The word soon received broad acceptance in industry and, in order to allow its free use, Yaskawa decided to abandon his rights on the word in 1982. The Mechatronics systems consist of components from different physical domains, which are closely coupled and therefore interact with one another. Moreover, the behavior of the components is highly non-linear.

Today it means mechatronics engineering activities including designing, testing and operation of machinery and equipment, in which there is a high level of functional integration of mechanical systems with electronics and computer control. Mechatronics is an interdisciplinary field, combining in a synergistic manner the classical knowledge of mechanical engineering, hydraulics, pneumatics, electronics, optics and computer science. A typical mechatronic system picks up signals from the environment, processes them to generate output signals, transforming them for example into forces, motions and actions. The aim of Mechatronics is to improve the functionality of technical systems and the creation of new concepts of machinery and equipment with built-in "artificial intelligence". Mechatronics provides an opportunity, not only humanization of machines, but also it changes the mindset and the approach to technological issues and most importantly teaching new technologies and ways of acquiring knowledge and skills. The most important feature of mechatronic devices is the ability to process and communicate information accurately in a form of different types of signals (mechanical, electrical, hydraulic, pneumatic, optical, chemical, biological), with high level of automation of these devices. Mechatronics Definition Mechatronics is the synergistic integration of sensors, actuators, signal conditioning, power electronics, decision and control algorithms, and computer hardware and software to manage complexity, uncertainty, and communication in engineered systems.IEEE (Institute of Electrical and Electronics Engineers) and ASME (American Society

Mechanical Engineers) promote the following definition: Mechatronics is the synergistic integration of mechanical engineering with the electronic control and the intelligent, PC- based control, in the design and manufacturing of goods and processes.

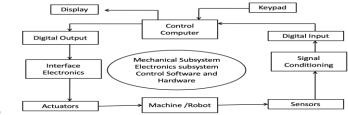

**Objectives Of Mechatronics**-echatronics has mainly the objective to improve technicalproperties, i.e., to make machines work faster and to make manufacturing cheaper. In industry, products and processes are designed fromscratch, and therefore they are known, and dealing with them is a kind of straightforward actionwhere the behavior can be predicted, at least in principle. Even there, however, the complexity oftasks and situations is increasing, leading already o the use of unconventional tools like fuzzy control,neural networks, expert systems, and their combinations. Figure shown the mechatronics industry system

**Mechatronics Design Step**-echatronic products are commonly used in industry and everyday life. Designing of mechatronic products requires aedicated approach that takes into account: interdisciplinary design, market related constraints, multifunctionality, user- friendly operation and demand of minimization of the cost of the whole product operation period. Thus designers who create mechatronic products should possess comprehensive interdisciplinary knowledge, ability to co-operate in an interdisciplinary designing team as well as team management skills, and knowledge how to use the up-to-date tools of computer aided engineering. Additionally the know-how in scheduling and carrying out prototyping of mechatronic systems is very useful.

### **Type of Elements**

Electromechanical elements: -

Sensors, A variety of physical variables can be measured using sensors. Actuators, DCservomotor, stepper motor, relay, solenoid, speaker, light emitting diode (LED), shape memory alloy, electromagnet, and pump apply commanded action on thephysical process.IC-based sensors and actuatorsdigital-compass, potentiometer, etc.

Fig: - Mechatronics Design Process ectrical elements:-

Electrical components e.g., resistor (R), capacitor (C), inductor (L), transformer, etc

#### **Electronic elements:-**

Analog/digital electronics, transistors, thyristors, opto-isolators, operationalamplifiers, power electronics, and signal conditioning.

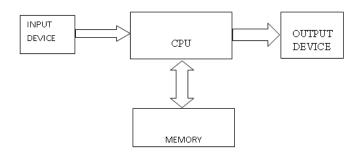

Control interface /computing hardware elements:-

**Analog-to-digital (A2D) converter**, digital-to-analog (D2A) converter, digitalinput/output (I/O), counters, timers,microprocessor, microcontroller, dataacquisition and control (DAC) board, and digital signal processing (DSP) board

Computer/Information System:-

Computer elements refer to hardware/software utilized to perform, computer- aided dynamic system analysis, optimization, design, and simulation, virtual instrumentation, rapid control prototyping, hardware-in-the-loop simulation, PC-based data acquisition and control

Elements of Mechatronics:-

Typical knowledgebase for optimal design and operation of mechatronic systems comprises of: Dynamic system modelling and analysis. Thermo-fluid, tructural, hydraulic, electrical, chemical, biological, etc. Decision and control theory, Sensors and signal conditioning, Actuators and power electronics, Data acquisition. A2D, D2A, digital I/O, counters, timers, etc. Hardware interfacing, Rapid control prototyping, Embedded computing.Balance theory, simulation, hardware, and software.

Mechatronics is the result of applying information systems to physical systems. The physical system, the rightmost dotted block, consists of mechanical, electrical, and computer (electronic) systems as well as actuators, sensors, and real time interfacing. Sensors and actuators are used to transduce energy from high power, usually the mechanical side, to lowpower, the electrical and computer or electronic side. The block labeled mechanical systemsfrequently consists of more than just mechanical components and may include fluid, pneumatic, thermal, acoustic, chemical, and other disciplines as well.

#### New Research Challenges

These interactively cooperating, intelligent machines lead to new research topics in the controltechniques of mechatronics and in other areas as well. It will be important that a machine and its components have learning capabilities, self- adaptation and self-calibration. Techniques such as the combination of neural networks, and fuzzy control with expert systems will further emphasize the importance of software.

#### Fig: – Elements of Mechatronics

Mechatronic Engineering is the engineering discipline concerned with the research, design, implementation and maintenance of intelligent engineered products and processes enabled by the integration of mechanical, electronic, computer, and software engineering technologiesSpecific expertise areas can include:

- Artificial Intelligence Techniques

- Avionics Computer Hardware and Systems Control Systems

- Data Communications and Networks

- Dynamics of Machines and Mechanisms

- Electromagnetic Energy Conversion

- ➢ Electronics

- Embedded & Real-time Systems

- Fluid Power and other Actuation Devices

- Human-Machine Interface Engineering and Ergonomics

- Industrial Automation

- Measurement, Instrumentation and Sensors

- Mechanical Design and Material Selection

- Mechatronic Design and System Integration

- Modelling and Simulation

- Motion Control

- Power Electronics

- Process Management, Scheduling, Optimization, and Control

- Process Plant and Manufacturing Systems

- Robotics

- Signal Processing

- Smart Infrastructure

- Software Engineering

- Systems Engineering

- > Thermofluids

- ➢ Haptic Interfaces

- Medicals

- > Automation

- $\succ$  Robotics

- > Control

- Mechanical Vibrations

- Mechatronics In Medicine

In 1985 the Department of Mechanical Engineering at Imperial College began research into medical robotics for neurosurgery. Further research into a robot for prostatectomy, commencing in 1988 culminated, in 1991, in a "World First" with the demonstration of robotic prostate

surgery. This robot was the first to actively remove tissue from a human patient in an operating theatre. With the expansion of robotic surgery applications, the Mechatronics in Medicine Laboratory was set up in 1993, as part of the Computer Aided Systems Engineering Section, to research and develop mechatronic aids to surgery. The group has developed mechatronic applications in fields as diverse as neurosurgery, magnetic resonance imaging (MRI) compatible robotics, haptic training systems for surgeons, urological

surgery and orthopaedics, high intensity focused ultrasound and blood sampling.

#### **New Applications**

i-VTEC, Micro Air Vehicles, Pistonless Pump, Multi Air Engine, Six Stroke Engine, Solar Cars, Thermo Acoustic Refrigeration, Biodeisel, Digital Twin Spark Ignition, Nano Enabled Coating Makes Aircraft Invisible, Automatic Transmission In Cars, Nitro Shock Absorbers, Hypercar, 3d Machine Vision Systems, Geothermal Energy, Cryogenic Heat Treatment, Next Generation 2-Stroke Engine, Microturbines, Next Generation Engines, Tidal Energy, Air Craft Hydraulic System, Cruise Missile Technology, Camless Engine, Automatic Vehicle Locator, Autonomous Car, Solar Energy Through Solar Space Stations, Anti-Lock Braking Sensors, Air Muscles, SkyBus Technology, Scramjet Engine, Pollution Less Engine, Paper Battery, Nano IC Engine, Liquid Nitrogen, Gasoline Direct Injection, Emulsified Ethanol, Direct Injection Diesel Engine, Vehicle Dynamics, Valvetronics, Tidal Power, Hovercraft, Infrared Curing and Convection Curing, Aeroplane Propulsion System, Running gearing, Fuel Energizer, GPS And Applications, Selective Laser Sintering, Agile Manufacturing, Cryocar, Cylinder deactivation, Dyna-cam engine, Apache Helicopter, CAMM Systems, Friction Stir Welding, HEMI engines, Just In Time Manufacturing, Lean manufacturing, Quality improvement tool "poka yoke", MEMS for Space, Personal Protection, Mine Detection Using Radar Bullets, Overall Equipment Effectiveness, Predictive Maintenance using Thermal Imaging, Methanol Fueled Marine Diesel Engine, Quality function deployment, Quasi turbine, Robots In Radioactive Environments, Sidewinder Missile, Smart Materials, Transit mxer & Concrete Pump, Turbofan Engine, Solar Sails, Ultrasonic Metal

Welding, The Hy-Wire Car, Thermal Barrier Coatings, Ultrasonic Techniques for hidden corrosion detection, Solar-powered vehicles, Two Stroke Engine Using Reed Valves, Vacuum Braking System, Variable Valve Timing In I.C. Engines, Space Elevator, Supercavitation, Thermal shock on interfacial adhesion of thermally conditioned, Total Productive Maintenance, Welding Robots, Air powered cars, Biomechatronic Hand, Computer Aided Process Planning, Re-entry of Space Vehicle, Sensotronic Brake Control, Skid Steer Loader and Multiterrain Loader, Space Robotics, Space Shuttles and its Advancements, Continuously variable transmission (CVT), Cryogenic grinding, Design, Analysis, Fabrication And Testing Of A Composite Leaf Spring, F1 Track Design and Safety, Green Engine, Head And Neck Support (HANS), Hydro Drive, Fractal Robots, Smart Bombs, Military Radars, Stealth Fighter, Handfree Driving, Solar Power Satellites (SPS), Nano Technology, Iontophoresis, Aerodynamics, Micro-Electromechanical Systems.

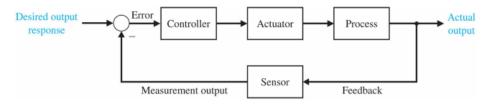

Sensors to measure the controlled variables. Sensors of all types provide the computer with information. it needs to perform monitoring and control tasks.

Actuators convert digital signals into physical or chemical quantities as required to correct errors in meeting the required performance.

Instrumentation subsystem.

This

involves all necessary signal-conditioning (SC) circuits to interface actuators, sensors, and other devices to the control computer.

Control computer. Proper control of a process requires intense processing of information representing a complex interplay between sensing the environmental conditions that affect the outcome of the process, interpretation of the sensed values, recognising effect of these values on the integrity of the operation, and initiating a response by signalling the actuators to take the necessary corrective actions. Coordinating all these activities is the responsibility of the control computer, which involves embedded microprocessor systems. it handles the flow of information between the various components by integrating the software and hardware dedicated to controlling the process in question. The hardware, also referred to as the target system, consists of all computers needed to manage the inputs and outputs of the mechatronic device. This includes sensors, actuators, mechanical components, power supplies, control computer, and the SC circuits interfacing the computer with the sensors and actuators. As a first step, a prototype of the hardware may be built using wire-wrapped boards to test the application software before the final product is realised. The software manages all activities of the target system. It consists of the program (or code), which is developed to meet the application requirement. Development of the application code can begin concurrently with the hardware prototype development once the system specifications have been completed. The code could be modified as it is developed to reflect design changes and/or new requirements as they emerge. The application code may be developed using machine language, assembly language, or a high-level language such as C. The machine code, or object code, contains binary codes that represent the instructions to the computer. It is the only language the microprocessor can understand and execute. High-level languages such as C use words and statements that are easily understood. A program written in a high-level language must be translated into executable machine language using a program called a compiler. Assembly language represents a middle ground between the extremes of machine language and the high-level language. An assembly language program is written using

mnemonics in which each statement corresponds to a machine instruction. The assembly program must be translated into machine language by a special program called an assembler.

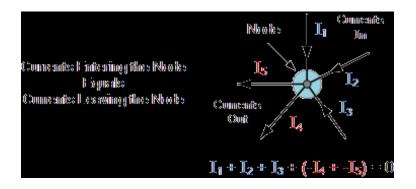

#### Kirchhoffs First Law – The Current Law, (KCL)

Kirchhoffs Current Law or KCL, states that the "total current or charge entering a junction or node is exactly equal to the charge leaving the node as it has no other place to go except to leave, as no charge is lost within the node". In other words the algebraic sum of ALL the currents entering and leaving a node must be equal to zero, I(exiting) + I(entering) = 0. This idea by Kirchhoff is commonly known as the Conservation of Charge.

Here, the three currents entering the node, I1, I2, I3 are all positive in value and the two currents leaving the node, I4 and I5 are negative in value. Then this means we can also rewrite the equation  $as_iI1 + I2 + I3 - I4 - I5 = 0$

The term Node in an electrical circuit generally refers to a connection or junction of two or more current carrying paths or elements such as cables and components. Also for current to flow either in or out of a node a closed circuit path must exist. We can use Kirchhoff's current law when analysing parallel circuits.

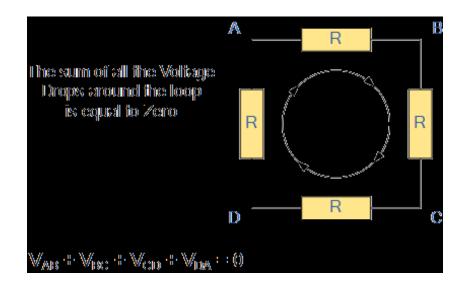

#### Kirchhoffs Second Law – The Voltage Law, (KVL)

Kirchhoffs Voltage Law or KVL, states that "in any closed loop network, the total voltage around the loop is equal to the sum of all the voltage drops within the same loop" which is also equal to zero. In other words the algebraic sum of all voltages within the loop must be equal to zero. This idea by Kirchhoff is known as the Conservation of Energy.

Starting at any point in the loop continue in the same direction noting the direction of all the voltage drops, either positive or negative, and returning back to the same starting point. It is important to maintain the same direction either clockwise or anti-clockwise or the final voltage sum will not be equal to zero. We can use Kirchhoff's voltage law when analysing series circuits. When analysing either DC circuits or AC circuits using Kirchhoff's Circuit Laws a number of definitions and terminologies are used to describe the parts of the circuit being analysed such as: node, paths, branches, loops and meshes. These terms are used frequently in circuit analysis so it is important to understand them.

Common DC Circuit Theory Terms:

- Circuit a circuit is a closed loop conducting path in which an electrical current flows.

- Path a single line of connecting elements or sources.

- Node a node is a junction, connection or terminal within a circuit were two or more circuit elements are connected or joined together giving a connection point between two or more branches. A node is indicated by a dot.

- Branch a branch is a single or group of components such as resistors or a source which are connected between two nodes.

- Loop a loop is a simple closed path in a circuit in which no circuit element or node is encountered more than once.

• Mesh - a mesh is a single closed loop series path that does not contain any other paths. There are no loops inside a mesh.

#### **Superposition Theorem**

The current through, or voltage across, an element in a linear bilateral network is equal to the algebraic sum of the currents or voltages produced independently by each source.

To consider the effects of each source independently requires that sources be removed and replaced without affecting the final result.

To remove a voltage source when applying this theorem, the difference in potential between the terminals of the voltage source must be set to zero (short circuit); removing a current source requires that its terminals be opened (open circuit). Any internal resistance or conductance associated with the displaced sources is not eliminated but must still be considered.

#### **THÉVENIN'S THEOREM**

The next theorem to be introduced, Thévenin's theorem, is probably one of the most interesting in that it permits the reduction of complex

networks to a simpler form for analysis and design. In general, the theorem can be used to do the following:

• Analyze networks with sources that are not in series or parallel.

• Reduce the number of components required to establish the same

characteristics at the output terminals.Investigate the effect of changing a particular component on the behavior of a network without having to analyze the entire network after each change.All three areas of application are demonstrated in the examples to follow.

Thévenin's theorem states the following:

Any two-terminal dc network can be replaced by an equivalent circuit consisting solely of a voltage source and a series resistor as shown in

### NORTON'S THEOREM

every voltage source with a series internal resistance has a current source equivalent. The current source equivalent can be determined by Norton's theorem (Fig. 9.64). It can also be

found through the conversions of Section 8.2. The theorem states the following: Any twoterminal linear bilateral dc network can be replaced by an quivalent circuit consisting of a current source and a parallel rsistor,

### Norton's Theorem Procedure

1. Remove that portion of the network across which the Norton euivalent circuit is found.

2. Mark the terminals of the remaining two-terminal networ

3. Calculate RN by first setting all sources to zero (voltage sources are rplaced with short circuits and current sources with openrcuits) and then finding the resultant resistance between the twomarked terminals. (If the internal resistance of the voltage and/orcurrent sources is included in the original network, it must remainwhen the sources are set to zero.) Since RN = RTh, the procedureand value obtained using the approach described for Thévenin'stheorem will determine the proper value of RN.IN:

4. Calculate IN by first returning all sources to their original position and then finding the shortcircuit current between the markedterminals. It is the same current that would be measured by anammeter placed between the marked terminals.Conclusion:

5. Draw the Norton equivalent circuit with the portion of the circuit previously removed replaced between the terminals of the equivalent

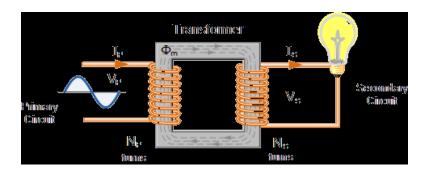

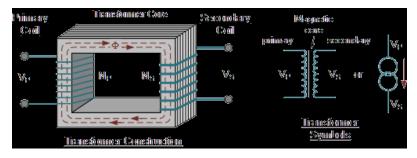

#### **Transformer Basics**

Transformers are electrical devices consisting of two or more coils of wire used to transfer electrical energy by means of a changing magnetic field oneof the main reasons that we use alternating AC voltages and currents in our homes and workplace's is that AC supplies can be easily generated at a convenient voltage, transformed (hence the name transformer) into much higher voltages and then distributed around the country using a national grid of pylons and cables over very long distances. The reason for transforming the voltage to a much higher level is that higher distribution voltages implies lower currents for the same power and therefore lower I2\*R losses along the networked grid of cables. These higher AC transmission voltages and currents can then be reduced to a much lower, safer and usable voltage level where it can be used to supply electrical equipment in our homes and workplaces, and all this is possible thanks to the basic Voltage Transformer.

The systems, used for data acquisition are known as data acquisition systems. These data acquisition systems will perform the tasks such as conversion of data, storage of data, transmission of data and processing of data.

```

MECHATRONIC SYSTEMS 5ME3-01

```

**Data acquisition systems**. Analog signals, which are obtained from the direct measurement of electrical quantities such as DC & AC voltages, DC & AC currents, resistance and etc. Analog signals, which are obtained from transducers such as LVDT, Thermocouple & etc.

Types of Data Acquisition Systems

Data acquisition systems can be classified into the following two types.

Analog Data Acquisition Systems

Digital Data Acquisition Systems

Now, let us discuss about these two types of data acquisition systems one by one.

Analog Data Acquisition Systems

The data acquisition systems, which can be operated with analog signals are known as analog data acquisition systems. Following are the blocks of analog data acquisition systems.

Transducer – It converts physical quantities into electrical signals.

Signal conditioner – It performs the functions like amplification and selection of desired portion of the signal.

Display device – It displays the input signals for monitoring purpose.

Graphic recording instruments – These can be used to make the record of input data permanently.

Magnetic tape instrumentation - It is used for acquiring, storing & reproducing of input data.

Digital Data Acquisition Systems

The data acquisition systems, which can be operated with digital signals are known as digital data acquisition systems. So, they use digital components for storing or displaying the information.

Mainly, the following operations take place in digital data acquisition.

Acquisition of analog signals

Conversion of analog signals into digital signals or digital data

Processing of digital signals or digital data

Following are the blocks of Digital data acquisition systems.

Transducer – It converts physical quantities into electrical signals.

Signal conditioner – It performs the functions like amplification and selection of desired portion of the signal.

Multiplexer – connects one of the multiple inputs to output. So, it acts as parallel to serial converter.

Analog to Digital Converter – It converts the analog input into its equivalent digital output.

Display device – It displays the data in digital format.

Digital Recorder – It is used to record the data in digital format.Data acquisition systems are being used in various applications such as biomedical and aerospace. So, we can choose either analog data acquisition systems or digital data acquisition systems based on the requirement.

### <u>UNIT 2</u>

Modeling, Analysis and Control of Physical Systems: Basics of System Modeling: LTI and LTV systems, Need for modeling, Types of modeling, Steps in modeling, Building blocks of models, Modelling of one and two degrees of freedom systems, Modeling of Electro-mechanical systems, Mechanical Systems, Fluid systems, Thermal systems; Dynamic Responses, System Transfer Functions, State Space Analysis and System Properties, Stability Analysis using Root Locus Method, Stability Analysis using Bode Plots, PID Controllers (with and without Time Delay

#### UNIT-2

#### **Modeling :**

control systems can be represented with a set of mathematical equations known as mathematical model. These models are useful for analysis and design of control systems. Analysis of control system means finding the output when we know the input and mathematical model. Design of control system means finding the mathematical model when we know the input and the output.

The following mathematical models are mostly used.

Differential equation model

Transfer function model

State space model

Let us discuss the first two models in this chapter.

**Differential Equation Model**

Differential equation model is a time domain mathematical model of control systems. Follow these steps for differential equation model.

Apply basic laws to the given control system.

Get the differential equation in terms of input and output by eliminating the intermediate variable(s).

#### Example

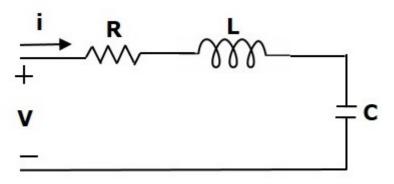

Consider the following electrical system as shown in the following figure. This circuit consists of resistor, inductor and capacitor. All these electrical elements are connected in series. The input voltage applied to this circuit is vi and the voltage across the capacitor is the output voltage vo.

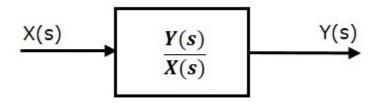

#### **Tansfer Function Model**

Transfer function model is an s-domain mathematical model of control systems. The Transfer function of a Linear Time Invariant (LTI) system is defined as the ratio of Laplace transform of output and Laplace transform of input by assuming all the initial conditions are zero.

If x(t) and y(t) are the input and output of an LTI system, then the corresponding Laplace transforms are X(s) and Y(s)

herefore, the transfer function of LTI system is equal to the ratio of Y(s) and X(s)

The transfer function model of an LTI system is shown in the following figure

Here, we represented an LTI system with a block having transfer function inside it. And this block has an input X(s) & output Y(s)

d2vodt2+(RL)dvodt+(1LC)vo=(1LC)vi

Apply Laplace transform on both sides.

s2Vo(s)+(sRL)Vo(s)+(1LC)Vo(s)=(1LC)Vi(s)

$\Rightarrow$ {s2+(RL)s+1LC}Vo(s)=(1LC)Vi(s)

$\Rightarrow$ Vo(s)Vi(s)=1LCs2+(RL)s+1LC

Where,

vi(s) is the Laplace transform of the input voltage vi

vo(s) is the Laplace transform of the output voltage vo

The above equation is a transfer function of the second order electrical system. The transfer function model of this system is shown below.

$$\frac{V_i(s)}{s^2 + \left(\frac{R}{L}\right)s + \frac{1}{LC}} \xrightarrow{V_o(s)}$$

ere, we show a second order electrical system with a block having the transfer function inside it. And this block has an input Vi(s) & an output Vo(s).

here are two types of mechanical systems based on the type of motion.

Translational mechanical systems

Rotational mechanical systems

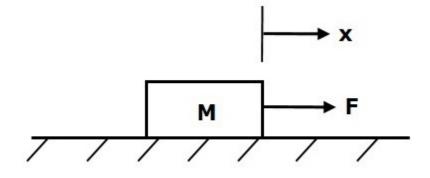

Modeling of Translational Mechanical Systems

Translational mechanical systems move along a straight line. These systems mainly consist of three basic elements. Those are mass, spring and dashpot or damper.

If a force is applied to a translational mechanical system, then it is opposed by opposing forces due to mass, elasticity and friction of the system. Since the applied force and the opposing forces are in opposite directions, the algebraic sum of the forces acting on the system is zero. Let us now see the force opposed by these three elements individually.

#### Mass

Mass is the property of a body, which stores kinetic energy. If a force is applied on a body having mass M, then it is opposed by an opposing force due to mass. This opposing force is

proportional to the acceleration of the body. Assume elasticity and friction are negligible

#### Fm∝a

$\Rightarrow$ Fm=Ma=Md2xdt2

F=Fm=Md2xdt2

Where,

F is the applied force

Fm is the opposing force due to mass

M is mass

a is acceleration

x is displacement

#### Spring

Spring is an element, which stores potential energy. If a force is applied on spring K, then it is opposed by an opposing force due to elasticity of spring. This opposing force is proportional to the displacement of the spring. Assume mass and friction are negligible.

#### **Modeling of Rotational Mechanical Systems**

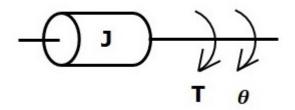

Rotational mechanical systems move about a fixed axis. These systems mainly consist of three basic elements. Those are moment of inertia, torsional spring and dashpot.

If a torque is applied to a rotational mechanical system, then it is opposed by opposing torques due to moment of inertia, elasticity and friction of the system. Since the applied torque and the opposing torques are in opposite directions, the algebraic sum of torques acting on the system is zero. Let us now see the torque opposed by these three elements individually.

Moment of Inertia

In translational mechanical system, mass stores kinetic energy. Similarly, in rotational mechanical system, moment of inertia stores kinetic energy.

If a torque is applied on a body having moment of inertia J, then it is opposed by an opposing torque due to the moment of inertia. This opposing torque is proportional to angular acceleration of the body. Assume elasticity and friction are negligible.

Tj∝α

$\Rightarrow$ Tj=J $\alpha$ =Jd2 $\theta$ dt2

T=Tj=Jd20dt2

Where,

T is the applied torque

Tj is the opposing torque due to moment of inertia

J is moment of inertia

$\alpha$  is angular acceleration

$\theta$  is angular displacement

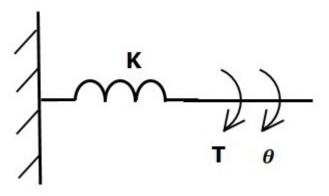

#### **Torsional Spring**

In translational mechanical system, spring stores potential energy. Similarly, in rotational mechanical system, torsional spring stores potential energy.

If a torque is applied on torsional spring K, then it is opposed by an opposing torque due to the elasticity of torsional spring. This opposing torque is proportional to the angular displacement of the torsional spring. Assume that the moment of inertia and friction are negligible.

Tk∝θ

$\Rightarrow$ Tk=K $\theta$

$T=Tk=K\theta$

Where,

T is the applied torque

Tk is the opposing torque due to elasticity of torsional spring

K is the torsional spring constant

$\theta$  is angular displacement

#### **Force Voltage Analogy**

In force voltage analogy, the mathematical equations of translational mechanical system are compared with mesh equations of the electrical system.

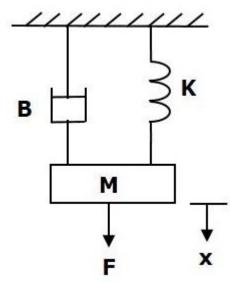

Consider the following translational mechanical system as shown in the following figure.

e force balanced equation for this system is

F=Fm+Fb+Fk

$\Rightarrow$ F=Md2xdt2+Bdxdt+Kx (Equation 1)

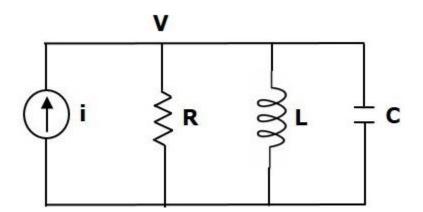

Consider the following electrical system as shown in the following figure. This circuit consists of a resistor, an inductor and a capacitor. All these electrical elements are connected in a series. The input voltage applied to this circuit is V volts and the current flowing through the circuit is i Amps.

Mesh equation for this circuit is

V=Ri+Ldidt+1cJidt (Equation 2)

Substitute, i=dqdt in Equation 2.

V=Rdqdt+Ld2qdt2+qC

$\Rightarrow$ V=Ld2qdt2+Rdqdt+(1c)q (Equation 3)

By comparing Equation 1 and Equation 3, we will get the analogous quantities of the translational mechanical system and electrical system. The following table shows these analogous quantities.

| Translational Mechanical System | Electrical System              |

|---------------------------------|--------------------------------|

| Force(F)                        | Voltage(V)                     |

| Mass(M)                         | Inductance(L)                  |

| Frictional Coefficient(B)       | Resistance(R)                  |

| Spring Constant(K)              | Reciprocal of Capacitance (1c) |

| Displacement(x)                 | Charge(q)                      |

| Velocity(v)                     | Current(i)                     |

Similarly, there is torque voltage analogy for rotational mechanical systems. Let us now discuss about this analogy.

| rotational Mechanical System       | Electrical System              |

|------------------------------------|--------------------------------|

|                                    |                                |

| Torque(T)                          | Voltage(V)                     |

|                                    |                                |

| Moment of Inertia(J)               | Inductance(L)                  |

|                                    |                                |

| Rotational friction coefficient(B) | Resistance(R)                  |

|                                    |                                |

| Torsional spring constant(K)       | Reciprocal of Capacitance (1c) |

|                                    |                                |

| Angular Displacement( $\theta$ )   | Charge(q)                      |

| Angular Velocity(ω) | Current(i) |

|---------------------|------------|

|                     |            |

#### **Force Current Analogy**

In force current analogy, the mathematical equations of the translational mechanical system are compared with the nodal equations of the electrical system.

Consider the following electrical system as shown in the following figure. This circuit consists of current source, resistor, inductor and capacitor. All these electrical elements are connected in parallel.

The nodal equation is

i=VR+1LJVdt+CdVdt (Equation 5)

Substitute, V=d $\Psi$ dt in Equation 5.

$i=1Rd\Psi dt+(1L)\Psi+Cd2\Psi dt2$

$\Rightarrow i = Cd2\Psi dt2 + (1R)d\Psi dt + (1L)\Psi (Equation 6)$

By comparing Equation 1 and Equation 6, we will get the analogous quantities of the

translational mechanical system and electrical system. The following table shows these analogous quantities.

| Translational Mechanical System | Electrical System            |

|---------------------------------|------------------------------|

| Force(F)                        | Current(i)                   |

| Mass(M)                         | Capacitance(C)               |

| Frictional coefficient(B)       | Reciprocal of Resistance(1R) |

| Spring constant(K)              | Reciprocal of Inductance(1L) |

| Displacement(x)                 | Magnetic Flux( $\psi$ )      |

| Velocity(v)                     | Voltage(V)                   |

Similarly, there is a torque current analogy for rotational mechanical systems. Let us now discuss this analogy.

Torque Current Analogy

In this analogy, the mathematical equations of the rotational mechanical system are compared with the nodal mesh equations of the electrical system.

By comparing Equation 4 and Equation 6, we will get the analogous quantities of rotational mechanical system and electrical system. The following table shows these analogous quantities.

| 1. Rotational Mechanical System       | <b>Electrical System</b>     |

|---------------------------------------|------------------------------|

| 2. Torque(T)                          | Current(i)                   |

| 3. Moment of inertia(J)               | Capacitance(C)               |

| 4. Rotational friction coefficient(B) | Reciprocal of Resistance(1R) |

| 5. Torsional spring constant(K)       | Reciprocal of Inductance(1L) |

| 6. Angular displacement( $\theta$ )   | Magnetic flux( $\psi$ )      |

| 7. Angular velocity( $\omega$ )       | Voltage(V)                   |

In this chapter, we discussed the electrical analogies of the mechanical systems. These analogies are helpful to study and analyze the non-electrical system like mechanical system from analogous electrical system.

#### **Response of the First Order System**

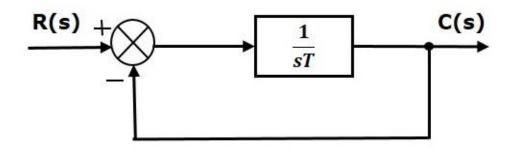

In this chapter, let us discuss the time response of the first order system. Consider the following block diagram of the closed loop control system. Here, an open loop transfer function, 1sT is connected with a unity negative feedback.

we know that the transfer function of the closed loop control system has unity negative feedback as,

C(s)R(s)=G(s)1+G(s)

Substitute, G(s)=1sT in the above equation.

C(s)R(s)=1sT1+1sT=1sT+1

The power of s is one in the denominator term. Hence, the above transfer function is of the first order and the system is said to be the first order system.

We can re-write the above equation as

C(s)=(1sT+1)R(s)

Where,

C(s) is the Laplace transform of the output signal c(t),

R(s) is the Laplace transform of the input signal r(t), and

T is the time constant.

Follow these steps to get the response (output) of the first order system in the time domain.

Take the Laplace transform of the input signal r(t).

Consider the equation, C(s)=(1sT+1)R(s)

Substitute R(s) value in the above equation.

Do partial fractions of C(s) if required.

Apply inverse Laplace transform to C(s).

In the previous chapter, we have seen the standard test signals like impulse, step, ramp and parabolic. Let us now find out the responses of the first order system for each input, one by one. The name of the response is given as per the name of the input signal. For example, the response of the system for an impulse input is called as impulse response.

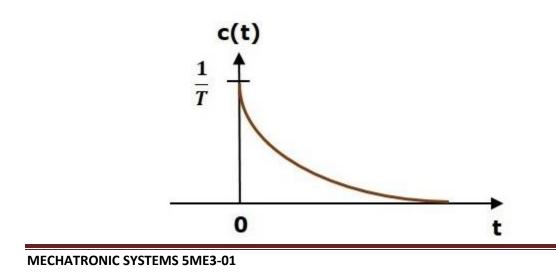

Impulse Response of First Order System

Consider the unit impulse signal as an input to the first order system.

So,  $r(t) = \delta(t)$

Apply Laplace transform on both the sides.

R(s)=1

Consider the equation, C(s)=(1sT+1)R(s)

Substitute, R(s)=1 in the above equation.

C(s)=(1sT+1)(1)=1sT+1

Rearrange the above equation in one of the standard forms of Laplace transforms.

$C(s)=1T(s+1T)\Rightarrow C(s)=1T(1s+1T)$

Apply inverse Laplace transform on both sides.

c(t)=1Te(-tT)u(t)

The unit impulse response is shown in the following figure.

**Page** 34

The unit impulse response, c(t) is an exponential decaying signal for positive values of 't' and it is zero for negative values of 't'.

Step Response of First Order System

Consider the unit step signal as an input to first order system.

So, r(t)=u(t)

Apply Laplace transform on both the sides.

R(s)=1s

Consider the equation, C(s)=(1sT+1)R(s)

Substitute, R(s)=1s in the above equation.

C(s) = (1sT+1)(1s) = 1s(sT+1)

Do partial fractions of C(s).

C(s)=1s(sT+1)=As+BsT+1

$\Rightarrow$ 1s(sT+1)=A(sT+1)+Bss(sT+1)

On both the sides, the denominator term is the same. So, they will get cancelled by each other. Hence, equate the numerator terms.

1=A(sT+1)+Bs

By equating the constant terms on both the sides, you will get A = 1.

Substitute, A = 1 and equate the coefficient of the s terms on both the sides.

$0=T+B\Rightarrow B=-T$

Substitute, A = 1 and B = -T in partial fraction expansion of C(s).

C(s)=1s-TsT+1=1s-TT(s+1T)

$\Rightarrow$ C(s)=1s-1s+1T

Apply inverse Laplace transform on both the sides.

c(t) = (1 - e - (tT))u(t)

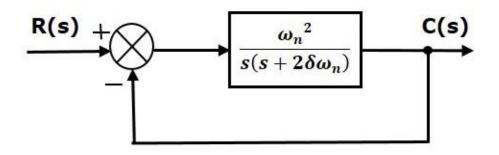

**Response of Second Order System**

let us discuss the time response of second order system. Consider the following block diagram of closed loop control system. Here, an open loop transfer function,  $\omega 2ns(s+2\delta\omega n)$  is connected with a unity negative feedback

e know that the transfer function of the closed loop control system having unity negative feedback as

C(s)R(s)=G(s)1+G(s)

Substitute,  $G(s)=\omega 2ns(s+2\delta\omega n)$  in the above equation.

$C(s)R(s) = (\omega 2ns(s+2\delta \omega n))1 + (\omega 2ns(s+2\delta \omega n)) = \omega 2ns2 + 2\delta \omega ns + \omega 2n$

The power of 's' is two in the denominator term. Hence, the above transfer function is of the second order and the system is said to be the second order system.

#### The characteristic equation is -

$s2+2\delta\omega ns+\omega 2n=0$

The roots of characteristic equation are -

$s=-2\omega\delta n\pm(2\delta\omega n)2-4\omega 2n----\sqrt{2}=-2(\delta\omega n\pm\omega n\delta 2-1----\sqrt{2})2$

$\Rightarrow$ s= $-\delta\omega$ n± $\omega$ n $\delta$ 2-1 $----<math>\sqrt{}$

The two roots are imaginary when  $\delta = 0$ .

The two roots are real and equal when  $\delta = 1$ .

The two roots are real but not equal when  $\delta > 1$ .

The two roots are complex conjugate when  $0 < \delta < 1$ .

We can write C(s) equation as,

$C(s) = (\omega 2ns2 + 2\delta \omega ns + \omega 2n)R(s)$

#### Where,

C(s) is the Laplace transform of the output signal, c(t)R(s) is the Laplace transform of the input signal, r(t)on is the natural frequency  $\delta$  is the damping ratio. Follow these steps to get the response (output) of the second order system in the time domain. Take Laplace transform of the input signal, r(t). Consider the equation,  $C(s) = (\omega 2ns2 + 2\delta \omega ns + \omega 2n)R(s)$ Substitute R(s) value in the above equation. Do partial fractions of C(s) if required. Apply inverse Laplace transform to C(s). Step Response of Second Order System Consider the unit step signal as an input to the second order system. Laplace transform of the unit step signal is, R(s)=1sWe know the transfer function of the second order closed loop control system is,  $C(s)R(s) = \omega 2ns2 + 2\delta \omega ns + \omega 2n$ Case 1:  $\delta = 0$ Substitute,  $\delta=0$  in the transfer function.

```

C(s)R(s)=\omega 2ns2+\omega 2n

```

```

\RightarrowC(s)=(\omega2ns2+\omega2n)R(s)

```

Substitute, R(s)=1s in the above equation.

$C(s) = (\omega 2ns2 + \omega 2n)(1s) = \omega 2ns(s2 + \omega 2n)$

Apply inverse Laplace transform on both the sides.

$c(t)=(1-cos(\omega nt))u(t)$

So, the unit step response of the second order system when /delta=0 will be a continuous time signal with constant amplitude and frequency.

Case 2:  $\delta = 1$

Substitute, /delta=1 in the transfer function.

$C(s)R(s)=\omega 2ns2+2\omega ns+\omega 2n$

$\Rightarrow$ C(s)=( $\omega$ 2n(s+ $\omega$ n)2)R(s)

Substitute, R(s)=1s in the above equation.

$C(s) = (\omega 2n(s + \omega n)2)(1s) = \omega 2ns(s + \omega n)2$

Do partial fractions of C(s).

$C(s)=\omega 2ns(s+\omega n)2=As+Bs+\omega n+C(s+\omega n)2$

After simplifying, you will get the values of A, B and C as 1,-1 and  $-\omega n$  respectively. Substitute these values in the above partial fraction expansion of C(s).

$C(s)=1s-1s+\omega n-\omega n(s+\omega n)2$

Apply inverse Laplace transform on both the sides.

$c(t)=(1-e-\omega nt-\omega nte-\omega nt)u(t)$

So, the unit step response of the second order system will try to reach the step input in steady state.

Case 3:  $0 < \delta < 1$

We can modify the denominator term of the transfer function as follows -

$s^2+2\delta\omega ns+\omega 2n=\{s^2+2(s)(\delta\omega n)+(\delta\omega n)^2\}+\omega 2n-(\delta\omega n)^2$

$=(s+\delta\omega n)2+\omega 2n(1-\delta 2)$

The transfer function becomes,

$C(s)R(s)=\omega 2n(s+\delta \omega n)2+\omega 2n(1-\delta 2)$

$\Rightarrow C(s) = (\omega 2n(s + \delta \omega n) 2 + \omega 2n(1 - \delta 2))R(s)$

Substitute, R(s)=1s in the above equation.

$C(s) = (\omega 2n(s + \delta \omega n) 2 + \omega 2n(1 - \delta 2))(1s) = \omega 2ns((s + \delta \omega n) 2 + \omega 2n(1 - \delta 2))$

Do partial fractions of C(s).

$C(s) = \omega 2ns((s + \delta \omega n)2 + \omega 2n(1 - \delta 2)) = As + Bs + C(s + \delta \omega n)2 + \omega 2n(1 - \delta 2)$

After simplifying, you will get the values of A, B and C as 1,-1 and  $-2\delta\omega n$  respectively. Substitute these values in the above partial fraction expansion of C(s).

$C(s)=1s-s+2\delta\omega n(s+\delta\omega n)2+\omega 2n(1-\delta 2)$

$C(s)=1s-s+\delta\omega n(s+\delta\omega n)2+\omega 2n(1-\delta 2)-\delta\omega n(s+\delta\omega n)2+\omega 2n(1-\delta 2)$

$C(s)=1s-(s+\delta\omega n)(s+\delta\omega n)2+(\omega n1-\delta 2\sqrt{2}-\delta 1-\delta 2\sqrt{(\omega n1-\delta 2\sqrt{(s+\delta\omega n)}2+(\omega n1-\delta 2\sqrt{2})2)})$

Substitute,  $\omega n 1 - \delta 2 - \dots - \sqrt{as \ \omega d}$  in the above equation.

$C(s)=1s-(s+\delta\omega n)(s+\delta\omega n)2+\omega 2d-\delta 1-\delta 2-\cdots -\sqrt{(\omega d(s+\delta\omega n)2+\omega 2d)}$

Apply inverse Laplace transform on both the sides.

$c(t) = (1 - e - \delta \omega nt \cos(\omega dt) - \delta 1 - \delta 2 - \dots - \sqrt{e - \delta \omega nt \sin(\omega dt)})u(t)$

$c(t) = (1 - e - \delta \omega nt 1 - \delta 2 - \dots - \sqrt{((1 - \delta 2 - \dots - \sqrt{)} \cos(\omega dt) + \delta \sin(\omega dt)))} u(t)$

If  $1-\delta 2-\cdots \sqrt{-\sin(\theta)}$ , then ' $\delta$ ' will be  $\cos(\theta)$ . Substitute these values in the above equation.

$c(t) = (1 - e^{-\delta\omega nt} 1 - \delta^2 - \cdots - \sqrt{(\sin(\theta)\cos(\omega dt) + \cos(\theta)\sin(\omega dt)))}u(t)$

$\Rightarrow c(t) = (1 - (e - \delta \omega nt 1 - \delta 2 - \dots - \sqrt{sin(\omega dt + \theta)})u(t)$

So, the unit step response of the second order system is having damped oscillations (decreasing amplitude) when ' $\delta$ ' lies between zero and one.

Case 4:  $\delta > 1$

We can modify the denominator term of the transfer function as follows -

$s^2+2\delta\omega ns+\omega 2n=\{s^2+2(s)(\delta\omega n)+(\delta\omega n)^2\}+\omega 2n-(\delta\omega n)^2$

$=(s+\delta\omega n)2-\omega 2n(\delta 2-1)$

The transfer function becomes,

$C(s)R(s)=\omega 2n(s+\delta \omega n)2-\omega 2n(\delta 2-1)$

$\Rightarrow$ C(s)=( $\omega$ 2n(s+ $\delta\omega$ n)2- $\omega$ 2n( $\delta$ 2-1))R(s)

Substitute, R(s)=1s in the above equation.

$C(s) = (\omega 2n(s + \delta \omega n)2 - (\omega n \delta 2 - 1\sqrt{2})(1s) = \omega 2ns(s + \delta \omega n + \omega n \delta 2 - 1\sqrt{2})(s + \delta \omega n - \omega n \delta 2 - 1\sqrt{2})$

Do partial fractions of C(s).

$C(s) = \omega 2ns(s + \delta \omega n + \omega n \delta 2 - 1 - \dots - \sqrt{})(s + \delta \omega n - \omega n \delta 2 - 1 - \dots - \sqrt{})$

$=\!\!As\!+\!Bs\!+\!\delta\omega n\!+\!\omega n\delta 2\!-\!1\!-\!\cdots\!-\!\sqrt{+}Cs\!+\!\delta\omega n\!-\!\omega n\delta 2\!-\!1\!-\!\omega n\delta 2\!-\!1\!-\omega n\delta 2\!-\omega n\delta 2\!-\!1\!-\omega n\delta 2\!-\omega n\delta 2\!-\omega$

After simplifying, you will get the values of A, B and C as 1,  $12(\delta+\delta 2-1\sqrt{)}(\delta 2-1\sqrt{)}$  and  $-12(\delta-\delta 2-1\sqrt{)}(\delta 2-1\sqrt{)}$  respectively. Substitute these values in above partial fraction expansion of C(s).

$C(s) = 1s + 12(\delta + \delta 2 - 1 - \dots - \sqrt{})(\delta 2 - 1 - \dots - \sqrt{})(1s + \delta \omega n + \omega n \delta 2 - 1 - \dots - \sqrt{}) - (12(\delta - \delta 2 - 1 - \dots - \sqrt{})(\delta 2 - 1 - \dots - \sqrt{}))(1s + \delta \omega n - \omega n \delta 2 - 1 - \dots - \sqrt{})$

Apply inverse Laplace transform on both the sides.

$c(t) = (1 + (12(\delta + \delta 2 - 1\sqrt{)}(\delta 2 - 1\sqrt{)})e^{-(\delta \omega n + \omega n \delta 2 - 1\sqrt{)}t - (12(\delta - \delta 2 - 1\sqrt{)}(\delta 2 - 1\sqrt{)})e^{-(\delta \omega n - \omega n \delta 2 - 1\sqrt{)}t})u }$ (t)

Since it is over damped, the unit step response of the second order system when  $\delta > 1$  will never reach step input in the steady state.

Impulse Response of Second Order System

The impulse response of the second order system can be obtained by using any one of these two methods.

Follow the procedure involved while deriving step response by considering the value of R(s) as 1 instead of 1s.

Do the differentiation of the step response.

The following table shows the impulse response of the second order system for 4 cases of the damping ratio.

**Construction of Root Locus** The root locus is a graphical representation in s-domain and it is symmetrical about the real axis. Because the open loop poles and zeros exist in the s-domain having the values either as real or as complex conjugate pairs. In this chapter, let us discuss how to construct (draw) the root locus.

Rules for Construction of Root Locus

Follow these rules for constructing a root locus.

Rule 1 – Locate the open loop poles and zeros in the 's' plane.

Rule 2 – Find the number of root locus branches.

We know that the root locus branches start at the open loop poles and end at open loop zeros. So,

the number of root locus branches N is equal to the number of finite open loop poles P or the number of finite open loop zeros Z, whichever is greater.

Mathematically, we can write the number of root locus branches N as

N=P if  $P \ge Z$

N=Z if P<Z

Rule 3 - Identify and draw the real axis root locus branches.

If the angle of the open loop transfer function at a point is an odd multiple of 1800, then that point is on the root locus. If odd number of the open loop poles and zeros exist to the left side of a point on the real axis, then that point is on the root locus branch. Therefore, the branch of points which satisfies this condition is the real axis of the root locus branch.

Rule 4 – Find the centroid and the angle of asymptotes.

If P=Z, then all the root locus branches start at finite open loop poles and end at finite open loop zeros.

If P>Z, then Z number of root locus branches start at finite open loop poles and end at finite open loop zeros and P-Z number of root locus branches start at finite open loop poles and end at infinite open loop zeros.

If P < Z, then P number of root locus branches start at finite open loop poles and end at finite open loop zeros and Z-P number of root locus branches start at infinite open loop poles and end at finite open loop zeros.

So, some of the root locus branches approach infinity, when  $P \neq Z$ . Asymptotes give the direction of these root locus branches. The intersection point of asymptotes on the real axis is known as centroid.

We can calculate the centroid  $\alpha$  by using this formula,

$\alpha = \sum Real part of finite open loop poles - \sum Real part of finite open loop zeros P-Z$

The formula for the angle of asymptotes  $\theta$  is

$\theta = (2q+1)1800P-Z$

Where,

q=0,1,2,...,(P-Z)-1

Rule 5 – Find the intersection points of root locus branches with an imaginary axis.

We can calculate the point at which the root locus branch intersects the imaginary axis and the

value of K at that point by using the Routh array method and special case (ii).

If all elements of any row of the Routh array are zero, then the root locus branch intersects the imaginary axis and vice-versa.

Identify the row in such a way that if we make the first element as zero, then the elements of the entire row are zero. Find the value of K for this combination.

Substitute this K value in the auxiliary equation. You will get the intersection point of the root locus branch with an imaginary axis.

Rule 6 - Find Break-away and Break-in points.

If there exists a real axis root locus branch between two open loop poles, then there will be a break-away point in between these two open loop poles.

If there exists a real axis root locus branch between two open loop zeros, then there will be a break-in point in between these two open loop zeros.

Note - Break-away and break-in points exist only on the real axis root locus branches.

Follow these steps to find break-away and break-in points.

Write K in terms of s from the characteristic equation 1+G(s)H(s)=0.

Differentiate K with respect to s and make it equal to zero. Substitute these values of s in the above equation.

The values of s for which the K value is positive are the break points.

Rule 7 – Find the angle of departure and the angle of arrival.

The Angle of departure and the angle of arrival can be calculated at complex conjugate open loop poles and complex conjugate open loop zeros respectively.

The formula for the angle of departure  $\phi d$  is

φd=1800−φ

The formula for the angle of arrival  $\phi a$  is

$\phi a=1800+\phi$

Where,

$\phi = \sum \phi P - \sum \phi Z$

Example

Let us now draw the root locus of the control system having open loop transfer function, G(s)H(s)=Ks(s+1)(s+5)

Step 1 – The given open loop transfer function has three poles at s=0,s=-1 and s=-5. It doesn't have any zero. Therefore, the number of root locus branches is equal to the number of poles of the open loop transfer function.

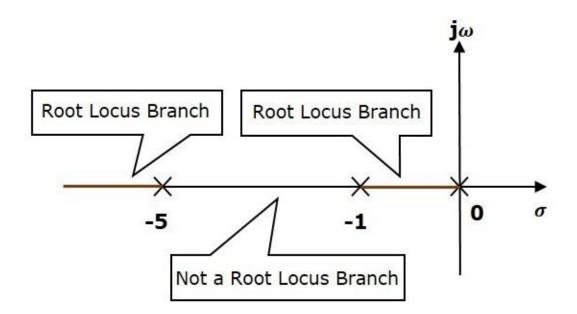

he three poles are located are shown in the above figure. The line segment between s=-1 and s=0 is one branch of root locus on real axis. And the other branch of the root locus on the real axis is the line segment to the left of s=-5.

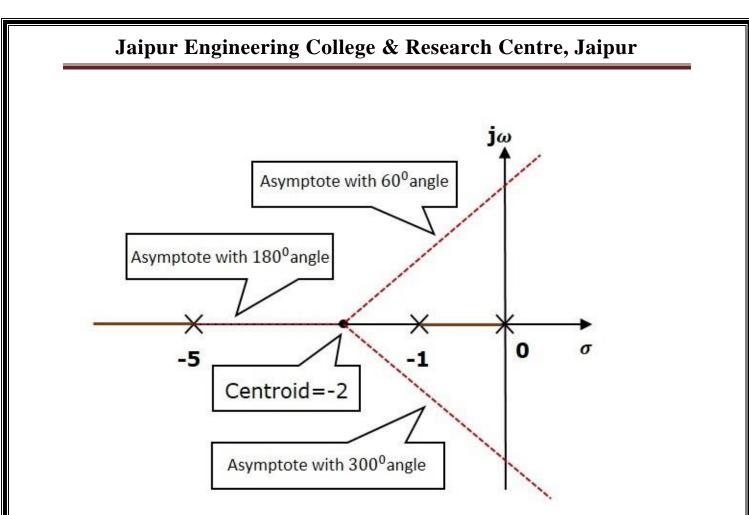

Step 2 - We will get the values of the centroid and the angle of asymptotes by using the given formulae.

Centroid  $\alpha = -2$

The angle of asymptotes are  $\theta$ =600,1800 and 3000.

The centroid and three asymptotes are shown in the following figure.

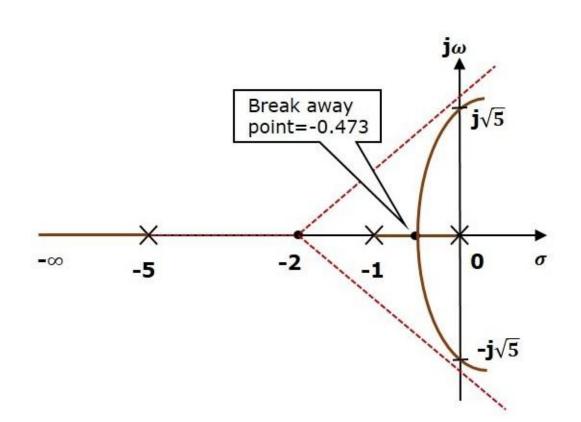

Step 3 – Since two asymptotes have the angles of 600 and 3000, two root locus branches intersect the imaginary axis. By using the Routh array method and special case(ii), the root locus branches intersects the imaginary axis at  $j5-\sqrt{}$  and  $-j5-\sqrt{}$ .

There will be one break-away point on the real axis root locus branch between the poles s=-1 and s=0. By following the procedure given for the calculation of break-away point, we will get it as s=-0.473.

The root locus diagram for the given control system is shown in the following figure.

n this way, you can draw the root locus diagram of any control system and observe the movement of poles of the closed loop transfer function.

From the root locus diagrams, we can know the range of K values for different types of damping.

Effects of Adding Open Loop Poles and Zeros on Root Locus

The root locus can be shifted in 's' plane by adding the open loop poles and the open loop zeros.

If we include a pole in the open loop transfer function, then some of root locus branches will move towards right half of 's' plane. Because of this, the damping ratio  $\delta$  decreases. Which implies, damped frequency  $\omega d$  increases and the time domain specifications like delay time td, rise time tr and peak time tp decrease. But, it effects the system stability.

If we include a zero in the open loop transfer function, then some of root locus branches will move towards left half of 's' plane. So, it will increase the control system stability. In this case, the damping ratio  $\delta$  increases. Which implies, damped frequency  $\omega d$  decreases and the time domain specifications like delay time td, rise time tr and peak time tp increase.

So, based on the requirement, we can include (add) the open loop poles or zeros to the transfer function.

#### **Control Systems - Controllers**

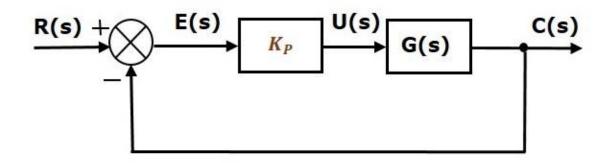

#### **Proportional Controller**

The proportional controller produces an output, which is proportional to error signal.

u(t)∝e(t)

$\Rightarrow$ u(t)=KPe(t)

Apply Laplace transform on both the sides -

U(s)=KPE(s)

U(s)E(s)=KP

Therefore, the transfer function of the proportional controller is KP.

Where,

U(s) is the Laplace transform of the actuating signal u(t)

E(s) is the Laplace transform of the error signal e(t)

KP is the proportionality constant

the block diagram of the unity negative feedback closed loop control system along with the proportional controller is shown in the following figure.

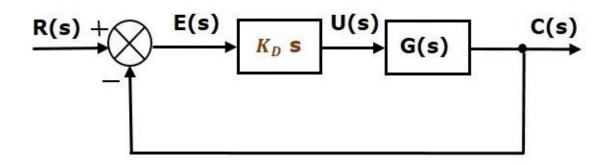

#### **Derivative Controller**

The derivative controller produces an output, which is derivative of the error signal.

u(t)=KDde(t)dt

Apply Laplace transform on both sides.

U(s)=KDsE(s)

U(s)E(s)=KDs

Therefore, the transfer function of the derivative controller is KDs.

Where, KD is the derivative constant.

The block diagram of the unity negative feedback closed loop control system along with the derivative controller is shown in the following figure.

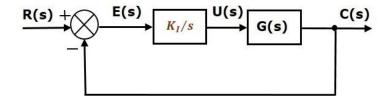

#### **Integral Controller**

The integral controller produces an output, which is integral of the error signal.

$u(t) = KI \int e(t) dt$

Apply Laplace transform on both the sides -

U(s)=KIE(s)s

U(s)E(s)=KIs

Therefore, the transfer function of the integral controller is KIs.

Where, KI is the integral constant.

The block diagram of the unity negative feedback closed loop control system along with the integral controller is shown in the following figure.

**MECHATRONIC SYSTEMS 5ME3-01**

**Page** 48

### <u>UNIT 3</u>

Sensors and Actuators: Static characteristics of sensors and actuators, Position, Displacement and Proximity Sensors, Force and torque sensors, Pressure sensors, Flow sensors, Temperature sensors, Acceleration sensors, Level sensors, Light sensors, Smart material sensors, Micro and Nano sensors, Selection criteria for sensors, Actuators: Electrical Actuators (Solenoids, Relays, Diodes, Thyristors, Triacs, BJT, FET, DC motor, Servo motor, BLDC motor, AC motor, Stepper motors), Hydraulic and Pneumatic actuators, *Design of Hydraulic and Pneumatic circuits, Piezoelectric actuators, Shape memory alloys.*

#### UNIT -3

#### Sensors

We live in a World of Sensors. You can find different types of Sensors in our homes, offices, cars etc. working to make our lives easier by turning on the lights by detecting our presence, adjusting the room temperature, detect smoke or fire, make us delicious coffee, open garage doors as soon as our car is near the door and many other tasks.All these and many other automation tasks are possible because of Sensors. Before going in to the details of What is a Sensor, What are the Different Types of Sensors and Applications of these different types of Sensors, we will first take a look at a simple example of an automated system, which is possible because of Sensors (and many other components as well).

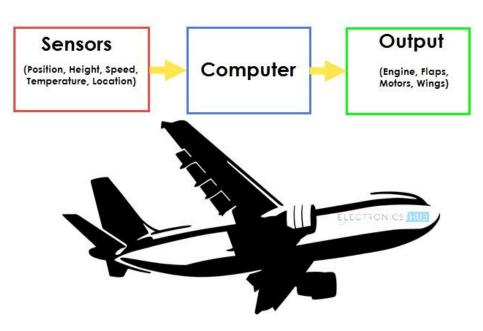

Real Time Application of Sensors

The example we are talking about here is the Autopilot System in aircrafts. Almost all civilian and military aircrafts have the feature of Automatic Flight Control system or sometimes called as

Autopilot.

An Automatic Flight Control System consists of several sensors for various tasks like speed control, height, position, doors, obstacle, fuel, maneuvering and many more. A Computer takes data from all these sensors and processes them by comparing them with pre-designed values.

The computer then provides control signal to different parts like engines, flaps, rudders etc. that help in a smooth flight. The combination of Sensors, Computers and Mechanics makes it possible to run the plane in Autopilot Mode.

All the parameters i.e. the Sensors (which give inputs to the Computers), the Computers (the brains of the system) and the mechanics (the outputs of the system like engines and motors) are equally important in building a successful automated system.

But in this tutorial, we will be concentrating on the Sensors part of a system and look at different concepts associated with Sensors (like types, characteristics, classification etc.).

What is a Sensor?

There are numerous definitions as to what a sensor is but I would like to define a Sensor as an input device which provides an output (signal) with respect to a specific physical quantity (input).

The term "input device" in the definition of a Sensor means that it is part of a bigger system which provides input to a main control system (like a Processor or a Microcontroller).

Another unique definition of a Sensor is as follows: It is a device that converts signals from one energy domain to electrical domain. The definition of the Sensor can be understood if we take an

**MECHATRONIC SYSTEMS 5ME3-01**

**Page** 50

example in to consideration.

#### **Classification of Sensors**

There are several classifications of sensors made by different authors and experts. Some are very simple and some are very complex. The following classification of sensors may already be used by an expert in the subject but this is a very simple classification of sensors.

In the first classification of the sensors, they are divided in to Active and Passive. Active Sensors are those which require an external excitation signal or a power signal.

Passive Sensors, on the other hand, do not require any external power signal and directly generates output response.

The other type of classification is based on the means of detection used in the sensor. Some of the means of detection are Electric, Biological, Chemical, Radioactive etc.

The next classification is based on conversion phenomenon i.e. the input and the output. Some of the common conversion phenomena are Photoelectric, Thermoelectric, Electrochemical, Electromagnetic, Thermooptic, etc.

The final classification of the sensors are Analog and Digital Sensors. Analog Sensors produce an analog output i.e. a continuous output signal with respect to the quantity being measured.

Digital Sensors, in contrast to Analog Sensors, work with discrete or digital data. The data in digital sensors, which is used for conversion and transmission, is digital in nature.

Different Types of Sensors

The following is a list of different types of sensors that are commonly used in various applications. All these sensors are used for measuring one of the physical properties like Temperature, Resistance, Capacitance, Conduction, Heat Transfer etc.

**Temperature Sensor**

**Proximity Sensor**

Accelerometer

IR Sensor (Infrared Sensor)

Pressure Sensor

Light Sensor

Ultrasonic Sensor

Smoke, Gas and Alcohol Sensor

Touch Sensor

Color Sensor

Humidity Sensor

Tilt Sensor

Flow and Level Sensor

We will see about few of the above mentioned sensors in brief. More information about the sensors will be added subsequently. A list of projects using the above sensors is given at the end of the page.

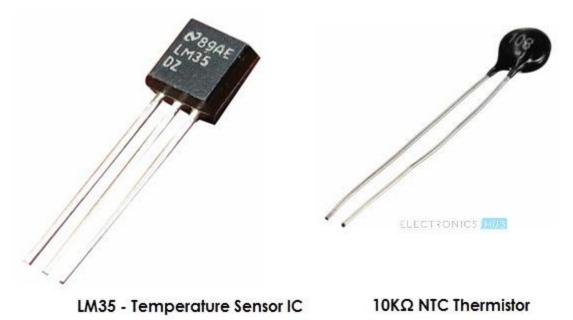

**Temperature Sensor**

One of the most common and most popular sensor is the Temperature Sensor. A Temperature Sensor, as the name suggests, senses the temperature i.e. it measures the changes in the temperature.

#### **Proximity Sensors**

A Proximity Sensor is a non-contact type sensor that detects the presence of an object. Proximity Sensors can be implemented using different techniques like Optical (like Infrared or Laser), Ultrasonic, Hall Effect, Capacitive, etc.

Some of the applications of Proximity Sensors are Mobile Phones, Cars (Parking Sensors), industries (object alignment), Ground Proximity in Aircrafts, etc.

Proximity Sensor in Reverse Parking is implemented in this Project: REVERSE PARKING SENSOR CIRCUIT.

Infrared Sensor (IR Sensor)

IR Sensors or Infrared Sensor are light based sensor that are used in various applications like Proximity and Object Detection. IR Sensors are used as proximity sensors in almost all mobile phones.

There are two types of Infrared or IR Sensors: Transmissive Type and Reflective Type. In Transmissive Type IR Sensor, the IR Transmitter (usually an IR LED) and the IR Detector (usually a Photo Diode) are positioned facing each other so that when an object passes between them, the sensor detects the object.

The other type of IR Sensor is a Reflective Type IR Sensor. In this, the transmitter and the detector are positioned adjacent to each other facing the object. When an object comes in front of the sensor, the sensor detects the object.

Different applications where IR Sensor is implemented are Mobile Phones, Robots, Industrial assembly, automobiles etc.

A small project, where IR Sensors are used to turn on street lights: STREET LIGHTS USING IR SENSORS.

Ultrasonic Sensor

An Ultrasonic Sensor is a non-contact type device that can be used to measure distance as well as velocity of an object. An Ultrasonic Sensor works based on the properties of the sound waves with frequency greater than that of the human audible range

Using the time of flight of the sound wave, an Ultrasonic Sensor can measure the distance of the object (similar to SONAR). The Doppler Shift property of the sound wave is used to measure the velocity of an object.

Arduino based Range Finder is a simple project using Ultrasonic Sensor: PORTABLE ULTRASONIC RANGE METER.

The following is a small list of projects based on few of the above mentioned Sensors.

Light Sensor – LIGHT DETECTOR USING LDR

Smoke Sensor – SMOKE DETECTOR ALARM CIRCUIT

Alcohol Sensor - HOW TO MAKE ALCOHOL BREATHALYZER CIRCUIT?

Touch Sensor – TOUCH DIMMER SWITCH CIRCUIT USING ARDUINO

Color Sensor - ARDUINO BASED COLOR DETECTOR

Humidity Sensor - DHT11 HUMIDITY SENSOR ON ARDUINO

Tilt Sensor - HOW TO MAKE A TILT SENSOR WITH ARDUINO?

In this article, we have seen about What is a Sensor, what are the classification of sensors and different Types of Sensors along with their practical applications.

#### Actuator

An actuator is a component of a machine that is responsible for moving and controlling a mechanism or system, for example by opening a valve. In simple terms, it is a "mover".