### **UNIT: 2 CPU**

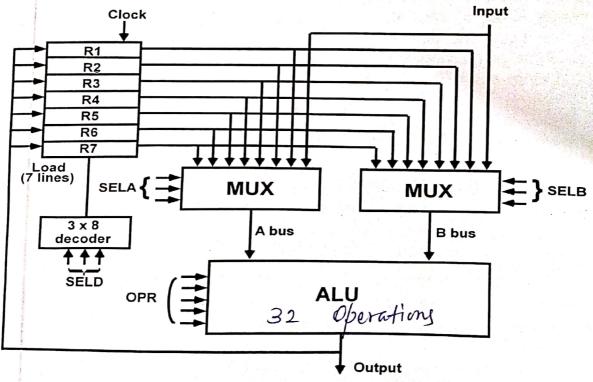

<u>GENERAL REGISTER ORGANISATION:</u> When a large number of registers are included in the CPU, it is most efficient to connect them through a common bus system. The registers communicate with each other not only for direct data transfers, but also while performing various micro-operations. Hence it is necessary to provide a common unit that can perform all the arithmetic, logic and shift micro-operation in the processor.

#### A Bus organization for seven CPU registers:-

The output of each register is connected to two multiplexer (mux) to form the two buses A & B. The selection lines in each multiplexer select one register or the input data for the particular bus. The A and B buses forms the input to a common ALU. The operation selected in the ALU determines the arithmetic or logic micro-operation that is to be performed. The result of the micro-operation is available for output and also goes into the inputs of the registers. The register that receives the information from the output bus is selected by a decoder. The decoder activates one of the register load inputs, thus providing a transfer both between the data in the output bus and the inputs of the selected destination register.

V Semester [2016-17] Page | 25

The control unit that operates the CPU bus system directs the ir flow through the registers and ALU by selecting the various comp the systems.

$$R_1 \rightarrow R_2 + R_3$$

(1) MUX A selection (SEC A): to place the content of R2 into bus

(2) MUX B selection (sec B): to place the content of R3 into bus E

(3)ALU operation selection (OPR): to provide the arithmetic addition

(4) Decoder destination selection (SEC D): to transfer the control output bus into R<sub>1</sub>

These form the control selection variables are generated in the coand must be available at the beginning of a clock cycle. The data two source registers propagate through the gates in the multiplexed ALU, to the output bus, and into the into of the destination region during the clock cycle intervals.

### **Control Word:**

There are 14 binary selection inputs in the units, and their combispecified a control word. It consists of four fields three fields combits each, and one field has five bits. The three bits of SEL A select register for the A input of the ALU. The three bits of SEL B select register for the B input of the ALU. The three bit of SEC D destination register using the decoder and its seven load outputs bits of OPR select one of the operations in the ALU. The 14-bit cor when applied to the selection inputs specify a particular micro-oper

## Table: Encoding of Register selection fields.

| Binary Code | SEL A          | SEL B          | SEL D          |

|-------------|----------------|----------------|----------------|

| 000         | Input          | / Input        | None           |

| 001         | $R_1$          | $R_1$          | $R_1$          |

| 010         | R <sub>2</sub> | R <sub>2</sub> | $R_2$          |

| 011         | R <sub>3</sub> | R <sub>3</sub> | R <sub>3</sub> |

| 100         | R <sub>4</sub> | R <sub>4</sub> | $R_4$          |

| 101         | R <sub>5</sub> | R <sub>5</sub> | R <sub>5</sub> |

| 110         | R <sub>6</sub> | R <sub>6</sub> | $R_6$          |

| 111         | R <sub>7</sub> | R <sub>7</sub> | $R_7$          |

## JAIPUR ENGINEERING COLLEGE AND RESEARCH CENTRE DEPARTMENT OF INFORMATION TECHNOLOGY

### Table: Encoding of ALU operation

| OPR & elect | Operation     | Symbol       |

|-------------|---------------|--------------|

| 00000       | Transfer A    | TSFA         |

| 00001       | Increment A   | INCA         |

| 00010       | Add A + B     | ADD          |

| 00101       | Subtract A-B  | SUB          |

| 00110       | Decrement A   | DEC A        |

| 01000       | AND A and B   | AND          |

| 01010       | OR A and B    | OR           |

| 01100       | XOR A and B   | XOR          |

| 01110       | Complement A  | COMA         |

| 10000       | Shift right A |              |

| 11000       | Shift left A  | SHRA<br>SHLA |

# Examples of Micro-operation for the CPU Symbolic Designation

| Micro Operation               | SECA           | SEC B          | SEL D          | OPR  | Cont | rol Wor<br>- S∈uß | d<br><i>.                                    </i> | OPR   |

|-------------------------------|----------------|----------------|----------------|------|------|-------------------|---------------------------------------------------|-------|

| $R_1 \rightarrow R_2 - R_3$   | R <sub>2</sub> | R <sub>3</sub> | R <sub>1</sub> | SUB  | 010  | 011               | 001                                               | 0010  |

| $R_4 \rightarrow R_{3} V R_5$ | R <sub>4</sub> | R              | R <sub>4</sub> | OR   | 100  | 101               | 100                                               | 01016 |

| $R_6 \rightarrow R_6 + 1$     | R <sub>6</sub> |                | R <sub>6</sub> | MCA  | 110  | 000               | 110                                               | 0000  |

| $R_7 \rightarrow R_1$         | R <sub>1</sub> | in the         | R <sub>7</sub> | TSFA | 001  | 000               | 111                                               | 0000  |

| Output ← R <sub>2</sub>       | R <sub>2</sub> | -              | None           | TSFA | 010  | 000               | 000                                               | 0000  |

| Output<->Input                | Input          |                | None           | TSFA | 000  | 000               | 000                                               | 0000  |

| R <sub>4</sub> → SHL R4       | R <sub>4</sub> | -              | R <sub>4</sub> | SHLA | 100  | 000               | 100                                               | 1100  |

| 5 → 0                         | R <sub>5</sub> | R <sub>5</sub> | R <sub>5</sub> | XOR  | 101  | 101               | 101                                               | 01100 |

V Semester

[2016-17]

**Stack Organization**

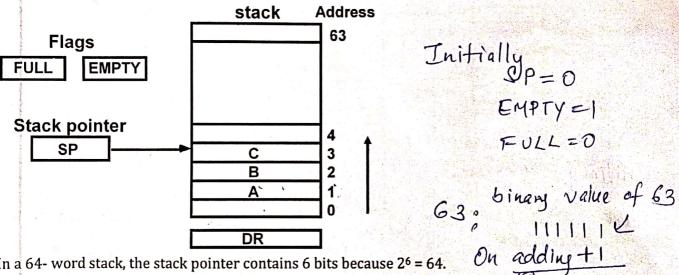

A useful feature that is included in the CPU of most computers is a stack or last-in first out (LIFO) list. A stack is a storage device that stores information in such a manner that the item stored last is the first item retrieved. The operation a stack can be companied to a stack of trays.

The stack in Digital Computer is essentially a memory unit with an address register that can count only (after an initial value is loaded into it.) The register that holds the address for the stack is called a Stack Pointer (SP) because its values always points at the top item in the stack.

The two operations - PUSH (insert) - Pop (delete)

Register Stack:- A stack can be placed in a portion of a large memory as it can be organized as a collection of a finite number of memory words as register.

In a 64- word stack, the stack pointer contains 6 bits because  $2^6 = 64$ . Discard 1000000

The one bit register FULL is set to 1 when the stack is full, and the one-bit register EMTY is set to 1 when the stack is empty. DR is the data register that holes the binary data to be written into on read out of the stack.

Initially, SP is decide to O, EMTY is set to 1, FULL = 0, so that SP points to the word at address O and the stack is masked empty and not full.

| PUSH SP | SP + 1 incr                                 | ement stack pointer                           |      |         |   |       |

|---------|---------------------------------------------|-----------------------------------------------|------|---------|---|-------|

|         | M [SP] ← DR                                 | unit item on top of the Stack                 |      | 34546 L |   |       |

|         | If $(SP = 0)$ then $EMTY \leftrightarrow 0$ | (FULL 1) check it stack is full               |      |         |   |       |

|         | EMILIA                                      | ma <b>s</b> k the stack not empty.            |      |         |   |       |

| POP     | DR <b>←M</b> [SP]<br>SP←SP -1               | read item trans the top of stack decrement SP | last | SP = 0  | ) | 00000 |

then (EMTY 1) check it stack is empty mark the stack not full.

Data

stack

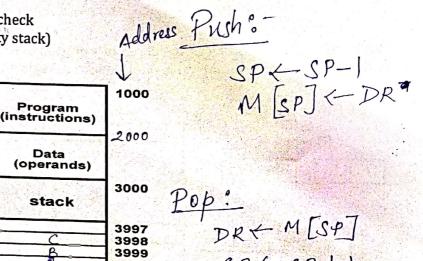

Memory stack: Memory with Program, Data, and Stack Segments

- A portion of memory is used as a stack with a processor register as a stack pointer

- PUSH:  $SP \leftarrow SP - 1$

- $M[SP] \leftarrow DR$

- POP:  $DR \leftarrow M[SP]$

- $SP \leftarrow SP + 1$

- · Most computers do not provide hardware to check stack overflow (full stack) or underflow(empty stack)

SPKSP+1

Initially, SP 40001

\* Most computer does not provide hardware to check full stack or empty Stack.

3999

4000 4001

REVERSE POLISH NOTATION

Arithmetic Expressions: A + B

- A + B Infix notation

- + A B Prefix or Polish notation

- A B + Postfix or reverse Polish notation

- The reverse Polish notation is very suitable for stack manipulation **Evaluation of Arithmetic Expressions**

Any arithmetic expression can be expressed in parenthesis-free Polish notation, including reverse Polish notation

V Semester

[2016-17]

#### Instruction Formats:

The most common fields found in instruction format are:-

An operation code field that specified the operation to be performed (1)

An address field that designates a memory address or a processor registers. (2)

A mode field that specifies the way the operand or the effective address is determined. (3)

Computers may have instructions of several different lengths containing varying number of addresses. The number of address field in the instruction format of a computer depends on the internal organization of its registers. Most computers fall into one of three types of CPU organization.

Single Accumulator organization ADD X AC → AC + M [×] (1)

General Register Organization ADD R1, R2, R3 R/← R2 + R3 (2)

PUSH X Stack Organization (3)

#### Three address Instruction

Computer with three addresses instruction format can use each address field to specify either processor register are memory operand.

ADD

$$R_1$$

, A, B  $A_1 \rightarrow M[A] + M[B]$

ADD

$$R_1$$

, A, B  $A_1 \rightarrow M$   $[A_1] \rightarrow M$   $[A_2] \rightarrow M$   $[C] + M$   $[B]$   $X = (A + B) * (C + A)$

$MULX, R_1, R_2 M [X] R_1 * R_2$

The advantage of the three address formats is that it results in short program when evaluating arithmetic expression. The disadvantage is that the binary-coded instructions require too many bits to specify three addresses.

#### **Two Address Instruction**

Most common in commercial computers. Each address field can specify either a processes register on a memory word.

| Uli a lilei | nory word.                      |                               |                       |

|-------------|---------------------------------|-------------------------------|-----------------------|

| MOV         | R <sub>1</sub> , A              | $R_1 \Rightarrow M[A]$        |                       |

| ADD         | R <sub>1</sub> , B              | $R_1 \rightarrow R_1 + M [B]$ |                       |

| MOV         | R <sub>2</sub> , C              | $R_2 \rightarrow M [C]$       | X = (A + B) * (C + D) |

| ADD         | $R_2$ , D                       | $R_2 \rightarrow R_2 + M [D]$ |                       |

| MUL         | R <sub>1</sub> , R <sub>2</sub> | $R_1 \rightarrow R_1 * R_2$   |                       |

| MOV         | X <sub>1</sub> R <sub>1</sub>   | $M[X] \rightarrow R_1$        |                       |

#### **One Address instruction**

It used an implied accumulator (AC) register for all data manipulation. For multiplication/division, there is a need for a second register.

| Heeu |                                                                               |                                                                                                                                                    |

|------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    |                                                                               |                                                                                                                                                    |

| В    | $AC \rightarrow AC + M [B]$                                                   | D 60 A)                                                                                                                                            |

| Т    | $M[T] \rightarrow AC$                                                         | $X = (A + B) \times (C + A)$                                                                                                                       |

| C    | 집 것이 있어 위원들이 어느로 가는 이 없는 것이 그런 아프리아 그리아는 전기를 하는 것을 받았다. 귀리아를 지나를 가득하는데 없다.    | All operations are done between the AC                                                                                                             |

| D    |                                                                               | register and a memory operand. It's the                                                                                                            |

| T    | 그렇게 하다면 얼마를 가득하다. 이 사람들은 그들은 그렇게 하는 그는 그렇게 되는 것이 되었다. 그 그렇게 살아먹다면 하루 없었다면 하다. | address of a temporary memory location                                                                                                             |

| X    | $M [\times] \rightarrow AC$                                                   | required for storing the intermediate result.                                                                                                      |

|      | A<br>B<br>T<br>C<br>D                                                         | B $AC \rightarrow AC + M[B]$<br>T $M[T] \rightarrow AC$<br>C $AC \rightarrow M(C)$<br>D $AC \rightarrow AC + M(D)$<br>T $AC \rightarrow AC + M(T)$ |

[2016-17] **V** Semester

### Zero - Address Instruction

A stack organized computer does not use an address field for the instruction ADD and MUL. The PUSH & POP instruction, however, need an address field to specify the operand that communicates with the stack (TOS → top of the stack)

| Ducu |   | T at the statett)                   |

|------|---|-------------------------------------|

| PUSH | A | $TOS \rightarrow A$                 |

| PUSH | В | TOS → B                             |

| ADD  |   | $TOS \rightarrow (A + B)$           |

| PUSH | C | TOS → C                             |

| PUSH | D | $TOS \rightarrow D$                 |

| ADD  |   | $TOS \rightarrow (C + D)$           |

| MUL  |   | $TOS \rightarrow (C + D) * (A + B)$ |

| POP  | X | M [X] ← TOS                         |

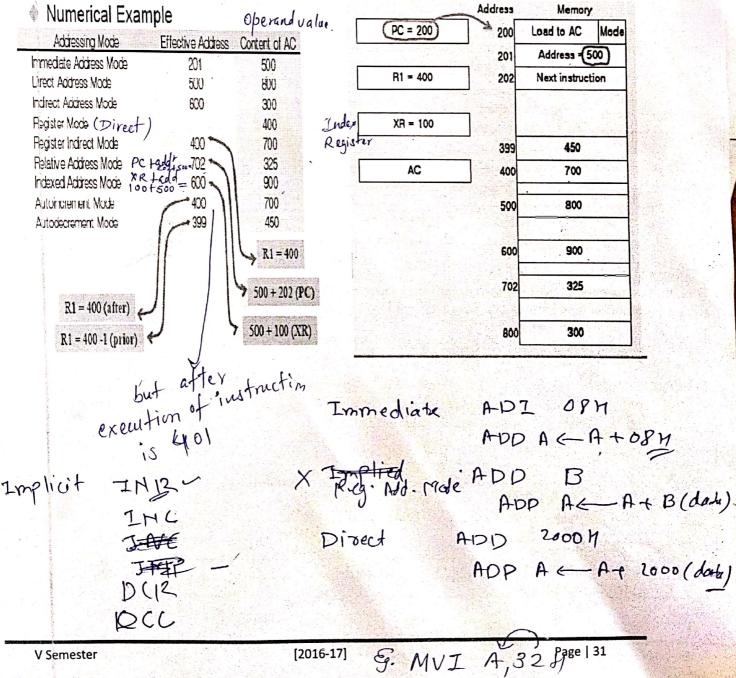

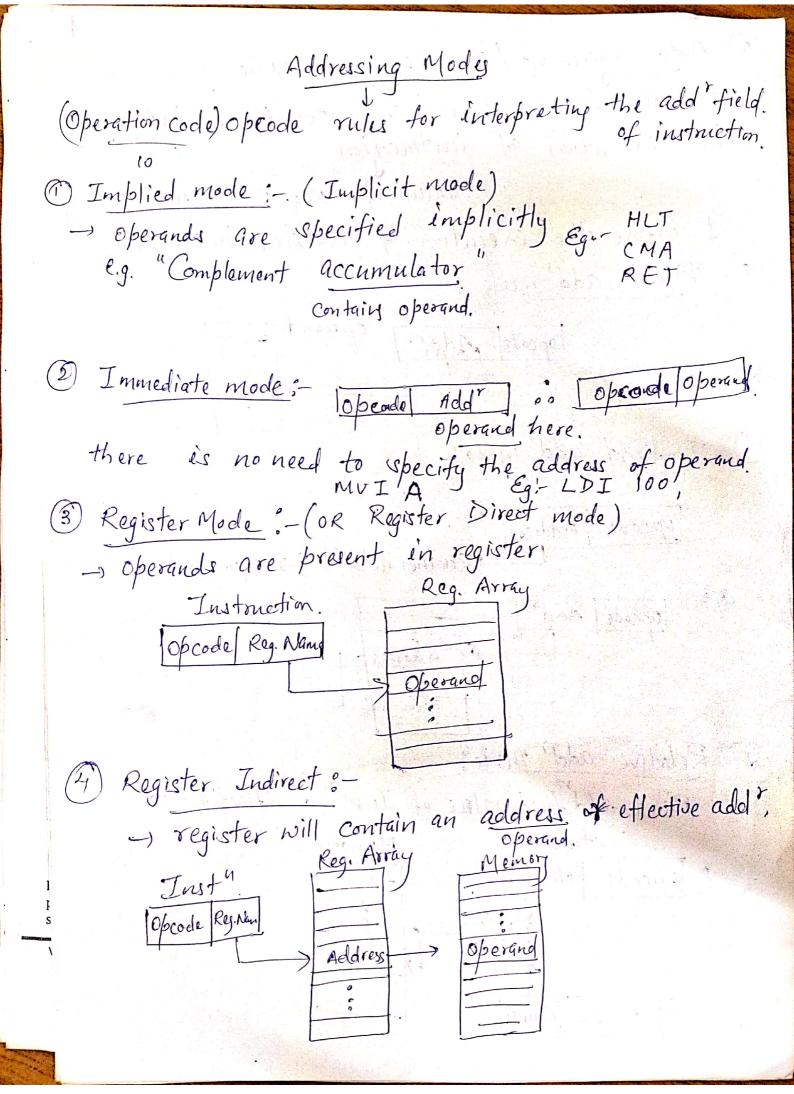

#### **Addressing Modes**

The operation field of an instruction specifies the operation to be performed. This operation must be executed on some data stored in computer register as memory words. The way the operands are chosen during program execution is dependent on the addressing mode of the instruction. The addressing mode specifies a rule for interpreting or modifying the address field of the instruction between the operand is activity referenced. Computer use addressing mode technique for the purpose of accommodating one or both of the following provisions.

- (1) To give programming versatility to the uses by providing such facilities as pointer to memory, counters for top control, indexing of data, and program relocation.

- (2) To reduce the number of bits in the addressing fields of the instruction.

#### The basic operation cycle of the computer

- (1) Fetch the instruction from memory

- (2) Decode the instruction

- (3) Execute the instruction

Program Counter (PC) keeps track of the instruction in the program stored in memory. PC holds the address of the instruction to be executed next and in incremented each time an instruction is fetched from memory.

(1) Implied mode

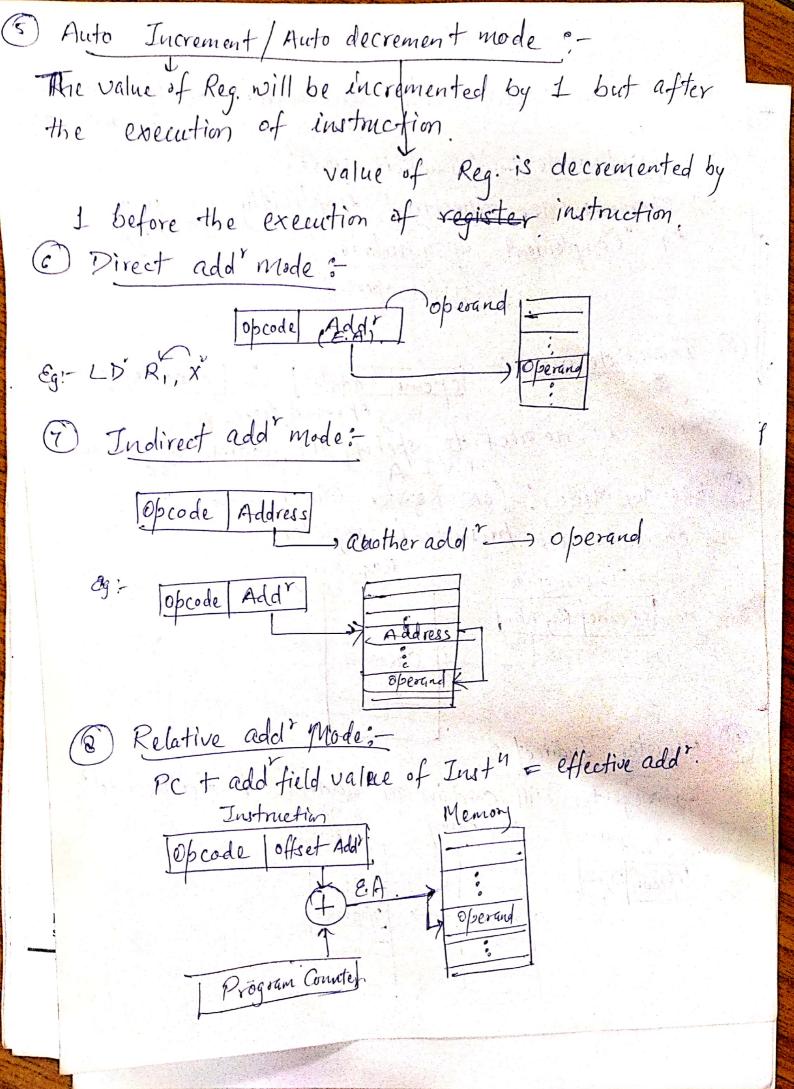

- (6) Auto increment/ Auto decrement mode

- (2) Immediate mode

- (7) Direct Address mode

(3) Register mode

(8) Indirect Address mode

(4) Register mode

- (9) Relative Address mode

- (5) Register indirect mode

- (10) Indexed Addressing mode

- (11) Base Register Addressing mode

| property and the same of the s |      | Name and Address of the Owner, where the Parket of the Owner, where the Owner, which is the Owner, whi | NAME AND ADDRESS OF THE OWNER, WHEN PERSON O | man and the second second second |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Opcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mode | To reside the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

#### Instruction format with mode field

V Semester [2016-17] Page | 30

**Relative Address:** The content of PC is added to the address part of the instruction in order to obtain the effective address Ex:- PC = 825 + 1 + 24

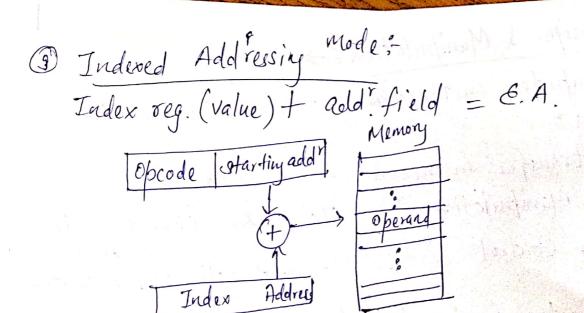

**Indexed addressing Mode:** The content of index register is added to the address part of the instruction in order to obtain the effective address.

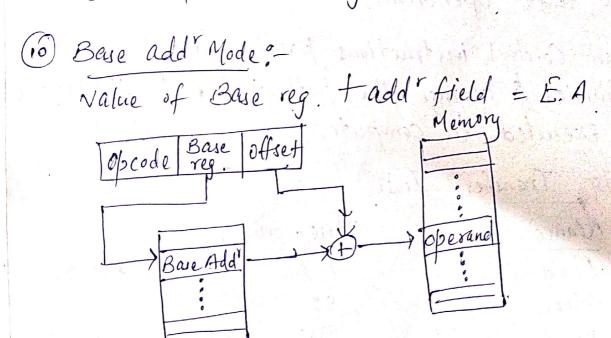

Base Register Addressing Mode:-The content of a base register is added to the address bank of the instruction to obtain the effective address.

#### Indirect Address:-

Effective Address = Address part of instruction + content of CPU register

#### JAIPUR ENGINEERING COLLEGE AND RESEARCH CENTRE DEPARTMENT OF INFORMATION TECHNOLOGY

### **Data Transfer & Manipulation**

Computer provides an extensive set of instructions to give the user the flexibility to carryout various computational task. Most computer instruction can be classified into three categories.

- (1) Data transfer instruction

- (2)Data manipulation instruction

- Program control instruction (3)

Data transfer instruction cause transferred data from one location to another without changing the binary instruction content. Data manipulation instructions are those that perform arithmetic logic, and shift operations. Program control instructions provide decision-making capabilities and change the path taken by the program when executed in the computer.

### (1) Data Transfer Instruction

Data transfer instruction move data from one place in the computer to another without changing the data content. The most common transfers are between memory and processes registers, between processes register & input or output, and between processes register themselves.

| (Typical data transfer instruction) |          |  |

|-------------------------------------|----------|--|

| Name                                | Mnemonic |  |

| Load                                | LD       |  |

| Store                               | ST       |  |

| Move                                | MOV      |  |

| Exchange                            | XCH      |  |

| Input                               | IN       |  |

| Output                              | OUT      |  |

| Push                                | PUSH     |  |

| Pop                                 | POP      |  |

#### (2) Data Manipulation Instruction

It performs operations on data and provides the computational capabilities for the computer. The data manipulation instructions in a typical computer are usually divided into three basic types.

- (a) Arithmetic Instruction

- Logical bit manipulation Instruction (b)

- (c) Shift Instruction.

#### (a) Arithmetic Instruction

| Name                    | Mnemonic |

|-------------------------|----------|

| Increment               | INC      |

| Decrement               | DEC      |

| Add                     | Add      |

| Subtract                | Sub      |

| Multiply                | MUL      |

| Divide                  | DIV      |

| Add with Carry          | ADDC     |

| Subtract with Basses    | SUBB     |

| Negate (2's Complement) | NEG      |

V Semester

[2016-17]

| (b) Logical & Bit Manipulation Instruction | ion      |

|--------------------------------------------|----------|

| Name                                       |          |

| Clear                                      | Mnemonic |

| Complement                                 | CLR      |

|                                            | COM      |

| AND                                        | AND      |

| OR                                         | OR       |

| Exclusive-Or                               | XOR      |

| Clear Carry                                | CLRC     |

| Set Carry                                  | SETC     |

| Complement Carry                           | COMC     |

| Enable Interrupt                           |          |

|                                            | ET       |

| Disable Interrupt                          | OI       |

#### (c) Shift Instruction

Instructions to shift the content of an operand are quite useful and one often provided in several variations. Shifts are operation in which the bits of a word are moved to the left or right. The bitshifted in at the and of the word determines the type of shift used. Shift instruction may specify

either logical shift, arithmetic shifts, or rotate type shifts.

| Name                      | Mnemonic |

|---------------------------|----------|

| Logical Shift right       | SHR      |

| Logical Shift left        | SHL      |

| Arithmetic shift right    | SHRA     |

| Arithmetic shift left     | SHLA     |

| Rotate right              | ROR      |

| Rotate left               | ROL      |

| Rotate mgmt through carry | RORC     |

| Rotate left through carry | ROLC     |

RISC & CISC ARCHITECTURE An important as bect of computer architecture

Characteristics of CISC architecture are: is the design of the instruction set for the procuso,

A large no. of instruction-typically from 100 to 250 instruction. (1)

Some instruction that perform specialized tasks and one used infrequently. (2)

A large variety of addressing modes - typically from 5 to 20 different modes. (3)

Variable length instruction format (4)

Instruction that manipulate operates in memory. (5)

#### RISC CHARACTERSTICS

The concept of RISC arithmetic involves an attempt to reduce execution time by simplifying the instruction set of the computer.

The major characteristics of a RISC processes are:

Relatively few instructions (1)

Relatively few addressing modes (2)

Memory access limited to load & store instruction (3)

All operations done within the registers of the CPU. (4)

## JAIPUR ENGINEERING COLLEGE AND RESEARCH CENTRE DEPARTMENT OF INFORMATION TECHNOLOGY

- Fixed-length, easily decoded instruction format (5)

- Single-cycle instruction execution (6)

- Handmaiden rather than micro programmed control. (7)

### **More RISC Characteristics**

- A relatively large numbers of registers in the processor unit.

- Compiler support: provides efficient translation of high-level language Programs into machine language programs.

### **Advantages of RISC**

- VLSI Realization

- Computing Speed

- Design Costs and Reliability

- High Level Language Support

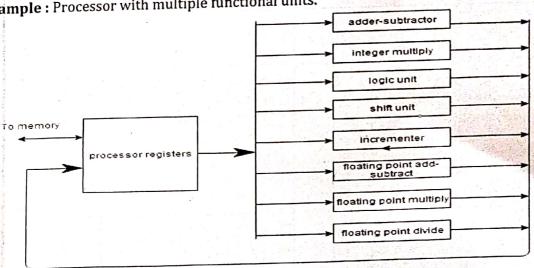

Parallel processing is a term used to denote a large class of techniques that are used to provide simultaneously data-processing tasks for the purpose of increasing the computational speed of the computer. Instead of processing each instruction sequentially as in a conventional computer, a parallel processing system is able to perform concurrent data processing to achieve faster execution time. The system may have two or more processor operating concurrently. The purpose of parallel processing is to speed up the computer processing capability and increase its throughput. The amount of hardware increases with parallel processing, hence the cost increases.

Example: Processor with multiple functional units.

PROCESSOR WITH MULTIPLE FUNCTIONAL UNITS

It shows one possible way of separating the execution unit into eight functional units operating in parallel. The operands in the registers are applied to one of the units depending on the operating specified by the instruction associated with the operand.

Page | 34 [2016-17] V Semester

Index Register

The add' field of the instruction provides the Starting add' of a data array in memory. The distance blu starting add' of the address of operand is the index value stored in index register.